Welcome to Apex Microtechnology. An industry leader in the power analog design of high voltage, high current and high speed power operational amplifiers and pulse width module (PWM) amplifiers. If you have ever needed an operational amplifier that was outside of main stream requirements, then you quite likely have already came across the Apex brand.

While Apex is recognized for excellence in precision power analog products for more than 30 years, we are not content to rest on our laurels. The introduction of new products and new technology concepts continues on course...as you would expect from a company that was founded and continues to grow through innovation.

To give you an overview on what we do, we will

- Start with a company introduction,

- Show examples of the markets we serve,

- Give a high level overview on the products we offer

- And discuss the value added resources we can provide

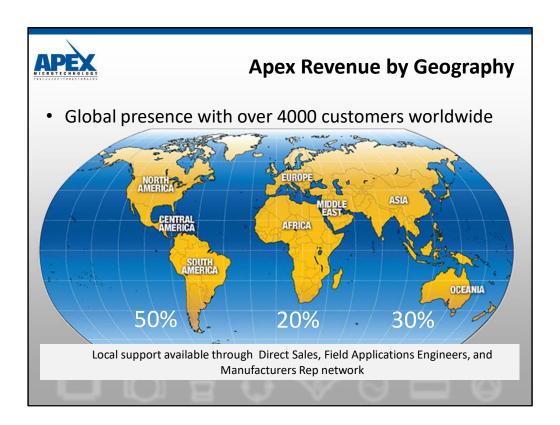

- Apex is well known around the global, servicing more than 3,200 customers world-wide

- Regional sales and engineering support and regional distribution centers ensures timely response to customer questions.

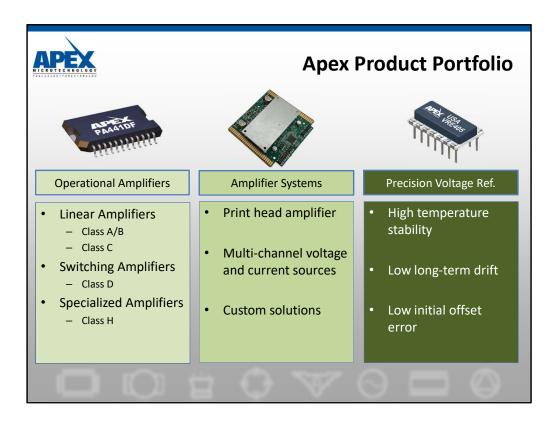

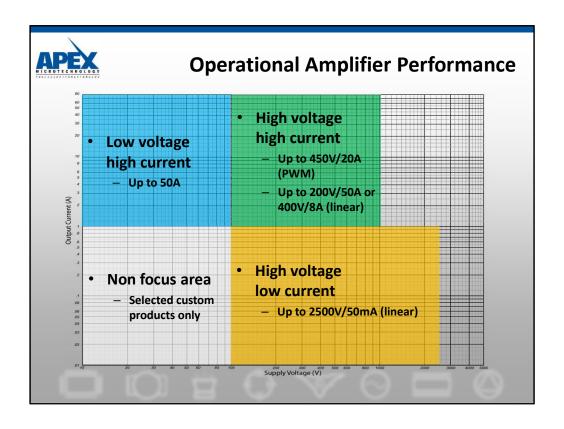

#### Apex is focusing on 3 products categories:

- Power operational amplifiers. Those are amplifiers that operate at high voltage, high current or high speed.

- Amplifier systems combine power operational amplifiers with digital content, providing high feature content on a small footprint.

- Apex's precision voltage references provide best in class performance in terms of temperature drift and long-term stability

Let's look at Apex's power operational amplifiers first:

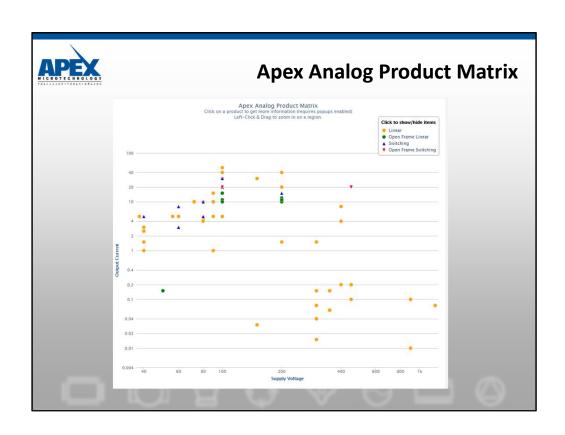

- Apex solutions support up to 2,500V supply voltage and 50A peak output current

- Besides current and voltage, Apex also offers high speed amplifiers, with slew rates up to 3,000V/µs

- Support for low-voltage and low output current products is limited, as this area is well served by other semiconductor companies.

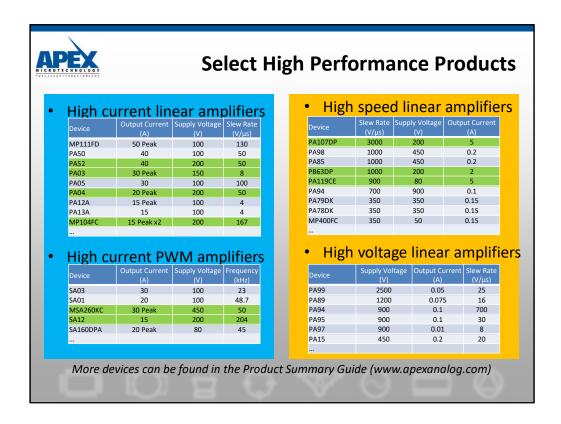

A limited selection of high performance products is shown on this slide. The product summary guide, available from the Apex web site, provides a good overview on all currently available products sorted by various categories.

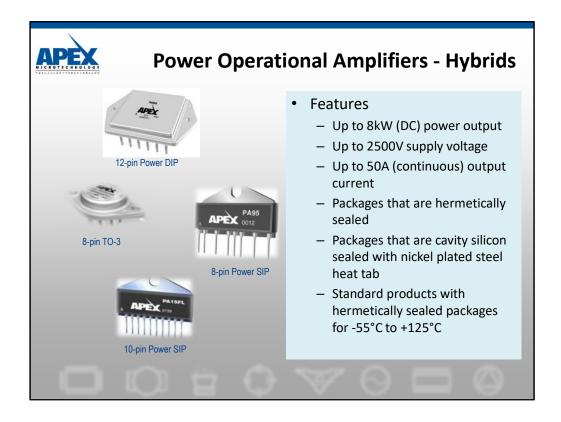

Now that you know more about what we do, let's show you how we do it. We mentioned that we offer power amplifiers and precision voltage references. Let's look at the power amplifiers first. These come in different flavors, ranging from hybrid designs to power ICs that are based on monolithic solutions.

- Hybrid devices are small circuits that are mounted within a single package. From the

outside there is no distinction between a hybrid device and a monolithic device, except

that that package might be larger. Package options include hermetically sealed metal

packages or plastic SIP packages.

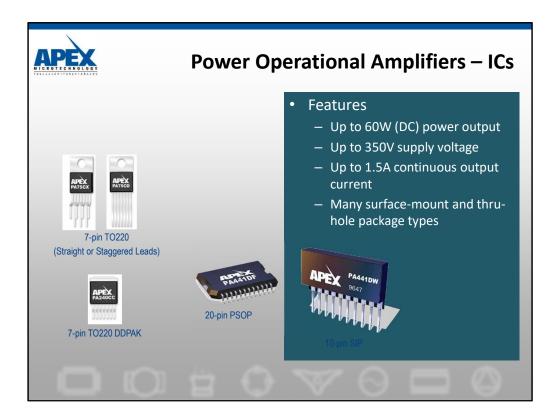

- Power ICs are monolithic circuits that are mounted in plastic packages

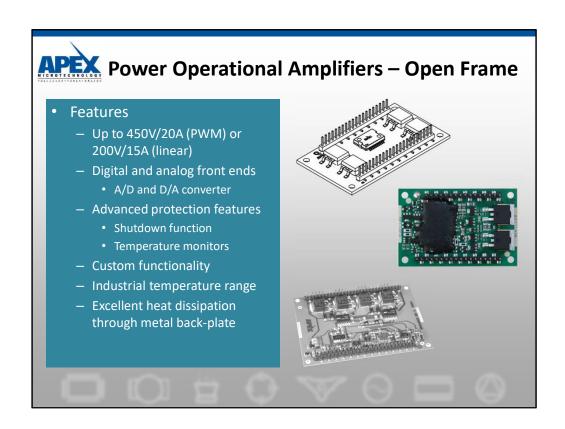

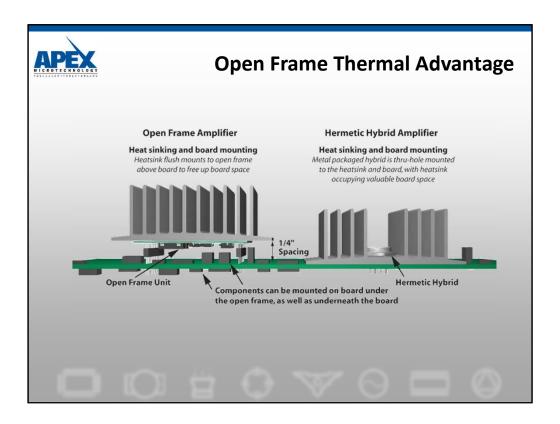

- Open Frames are small circuits that are surface mounted on an insulated aluminum frame.

Hybrid packages are typically the most robust packages available. They are also the most complicated and most costly devices, as the limited space demands the use of bare die assembly techniques and special production technologies.

Open frames provide the best flexibility and the shortest development time, They offer high functionality as do the hybrid packages but operate within industrial temp ranges. Power ICs are what is most commonly used in the semiconductor industry. However, there are limits in terms on functionality and device parameters

Apex's hybrid amplifier products provide leading edge characteristics, either in terms of power output, supply voltage or speed. They are used in the most demanding of applications. The option of a hermetically sealed package allows the use of the devices in applications where high reliability and robust performance are key design considerations.

Open frame products offer the ability to add digital and custom content on a platform that provides excellent heat dissipation capabilities.

Power ICs are the lowest cost product options, but are limited in terms of output current and supply voltage. However, we still talk leading edge technology here, as there are only a few suppliers that provide amplifiers that can operate in the 350V range. Packaging varies from very small PSOP and TO-220 packages, to the SIP packages that are also used to house some of the hybrid amplifiers Apex sells.

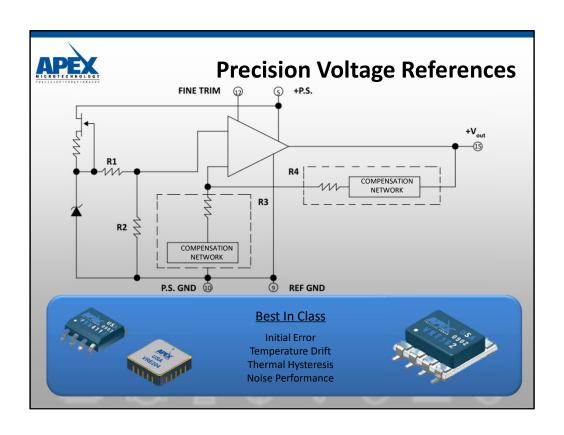

## **Precision Voltage References**

Best-in-class performance for initial error, temperature drift, thermal hysteresis and noise performance

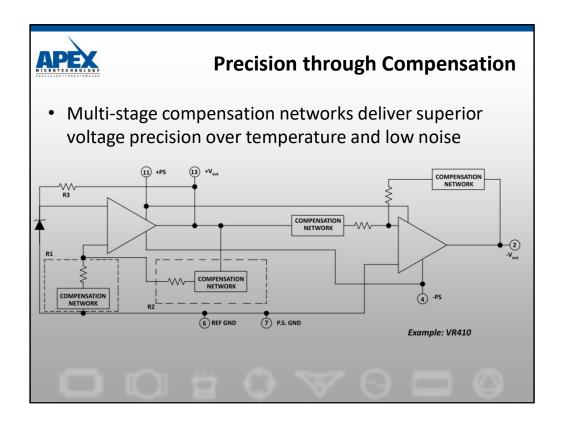

The other major product family offered by Apex are the industry's best-in-class precision voltage references (VREs). While there is a wealth of voltage references available as monolithic designs, the Apex product line are typically selected when initial error, temperature drift and long-term stability are critical design requirements.

This best-in-class performance is the result of very labor intensive production. Various compensation networks that need to go through an iterative trimming process ensure that the resulting reference output meets and exceeds the device specifications. Voltage reference are available as single or dual output. The VRE410, shown in this example, offers +10V and -10V output within a single 14-pin package.

## **Precision Voltage References**

- 25 <u>precision</u> voltage references

- Zener based with 3<sup>rd</sup>-order compensation voltage references

- Functionally equivalent to 3-terminal regulator

- Total error over 25 / +85C as low as 0.5 PPM / C

- Several supply voltage and reference output options

- 1.25V, 2.5V, 3V, 4.5V, 5V, 6V, and 10V References

- Very unique feature set

- Positive/Negative and dual outputs available

# Not Self-Heating!

#### Precision Reference Target Applications

- Precision A/D and D/A converters

- Transducer excitation

- Accurate comparator threshold reference

- High resolution servo systems

- Digital voltmeters

- High-precision test and measurement instruments

- High-precision ATE system and instrument calibration modules

# **VRE 100/200 Product Families**

• Highest Performance References Available Anywhere

- Initial Error: .005%

- Noise: 0.3ppm (0.1-10Hz)

– Temperature Coefficient: 0.5ppm/ºC

• Hi Reliability Construction

MIL Temp Range

- 100% Burn-In

Ceramic Packages

# **VRE 300/400 Product Families**

- High Performance Industrial References

- Initial Error: .01%

- Noise: 0.3ppm (0.1-10Hz)

- Temperature Coefficient: 0.6ppm/ ºC

14-pin DIP

- Graded Performance

- Plastic DIP and SMT packages

- Commercial (0/70C) and Industrial (-25/85C) Temp Range

Mount

| PEROTECHNOL | DGY        | Vol                | Voltage Reference Product Overvi |              |                              |  |  |  |  |  |  |

|-------------|------------|--------------------|----------------------------------|--------------|------------------------------|--|--|--|--|--|--|

| MODEL       | Output (V) | Initial Error (mV) | Temp Coefficient (ppm/°C)        | Noise (μVpp) | Features                     |  |  |  |  |  |  |

| /RE102      | ±10        | 1.0, 1.2, 1.5, 1.7 | 1.09, 1.11, 1.33, 1.45           | 6            | High Rel Military            |  |  |  |  |  |  |

| /RE104      | 4.5        | 0.8, 0.9           | 1.48, 1.62, 1.70, 1.98           | 3            | High Rel Military            |  |  |  |  |  |  |

| /RE107M     | ±5         | 0.8, 0.9           | 1.33, 1.56                       | 3            | High Rel Military            |  |  |  |  |  |  |

| /RE204M     | 4.5        | 0.8, 0.9           | 1.48, 1.70                       | 3            | Small Pkg, High Rel Military |  |  |  |  |  |  |

| /RE205      | 5          | 0.8,0.9            | 1.33, 1.45, 1.56, 1.82           | 3            | Small Pkg, High Rel Military |  |  |  |  |  |  |

| /RE210      | 10         | 0.5, 0.7, 0.8, 1.0 | 1.09, 1.11, 1.33, 1.45           | 6            | Small Pkg, High Rel Military |  |  |  |  |  |  |

| /RE302      | 2.5        | 0.4, 0.6           | 1.0, 2.2                         | 1.5          | Low Cost                     |  |  |  |  |  |  |

| /RE304      | 4.5        | 0.45, 0.9          | 0.6, 2.0                         | 3            | Low Cost                     |  |  |  |  |  |  |

| /RE305      | 5          | 0.5, 0.8, 1.0      | 0.6, 1.0, 2.0                    | 3            | Low Cost                     |  |  |  |  |  |  |

| /RE306      | 6          | 0.6, 1.2           | 0.6, 2.0                         | 4            | Low Cost                     |  |  |  |  |  |  |

| /RE310      | 10         | 1.0, 1.6, 2.0      | 0.6, 1.0, 2.0                    | 6            | Low Cost                     |  |  |  |  |  |  |

| /RE410      | ±10        | 1.6, 2.0, 2.2      | 1.0, 2.0, 2.2                    | 6            | Dual, Low Cost               |  |  |  |  |  |  |

| /RE3025     | 2.5        | 0.25, 0.375, 0.5   | 0.6, 1.0, 2.0                    | 1.5          | +10 V Supply                 |  |  |  |  |  |  |

| /RE3050     | 5          | 0.5, 0.8, 1.0      | 0.6, 1.0, 2.0                    | 3            | +10 V Supply                 |  |  |  |  |  |  |

| /RE3041     | 4.096      | 2.0                | 1.0                              | 3            | Low Drift                    |  |  |  |  |  |  |

| SWR200      | 7.071 RMS  | 0.5%               | 20                               | 0.05% THD    | Sine wave reference          |  |  |  |  |  |  |

The table shows the available precision voltages and the grade choices for initial error and temperature coefficient.

## **Seminar Topics**

- Op Amps

- <u>Safe Operating Area</u>

- Single Supply Operation

- <u>Stability and Compensation</u>

- PWM Basics

- Basic PWM Transfer Function

- Biasing PWM Systems

- Low Pass Filter Response

- ATE Audio

- Deflection

- <u>High Power Techniques</u>

- Motion Control

- Piezo Drive Applications

- Conclusion

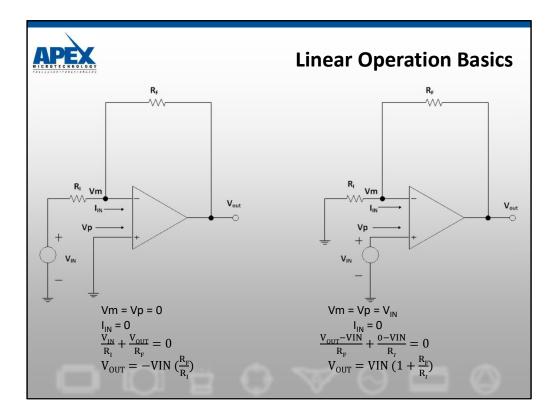

Three most important characteristics of an ideal op amp are: 1) infinite input impedance

- 2) zero output impedance

- 3) infinite open loop gain

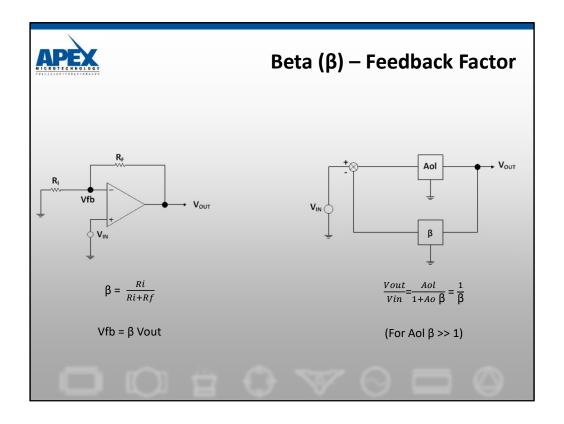

Let's review the inverting configuration in light of these three basic characteristics. #1 dictates that the input current into the op amp is 0. #3 implies that any voltage appearing between the input terminals will result in infinite output voltage. The resistive divider action of Rf and Ri causes a portion of the output voltage to be fed back to the inverting input. It is this NEGATIVE FEEDBACK action coupled with #3, open loop gain, that keeps the voltage between the two inputs at zero.

In the inverting configuration, this results in a "virtual ground" node. The concept of a virtual ground, coupled with the zero input current flow, allows the "closed loop gain" or transfer function of the circuit to be easily calculated. Current flow in Ri is equal to Vin/Ri. The same current is forced to flow through Rf, giving an output voltage of -linRf.

In the non-inverting amplifier, the infinite open loop gain of the amplifier, coupled with negative feedback, force the inverting terminal to be equal to the non-inverting terminal. This sets up a voltage across Ri which develops a current that also flows through Rf. Therefore, the total output voltage is s Vin/Rin current times the series combination of Rf and Ri.

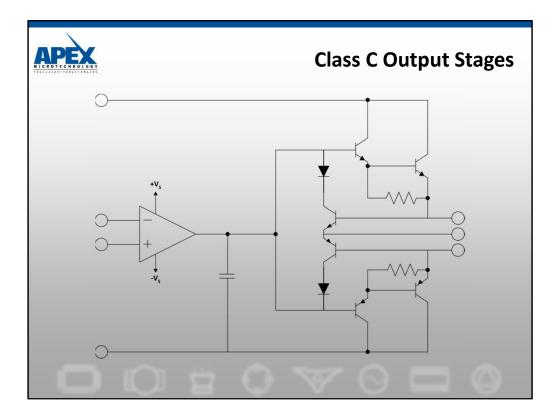

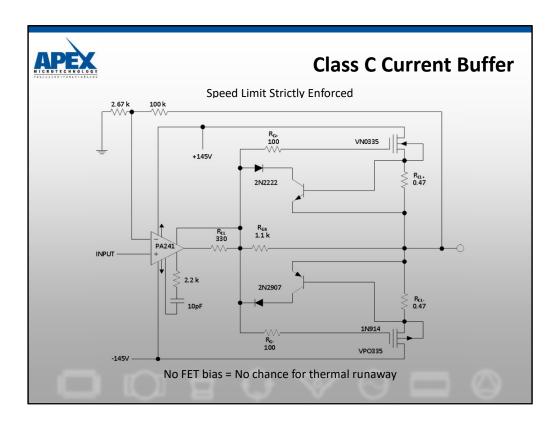

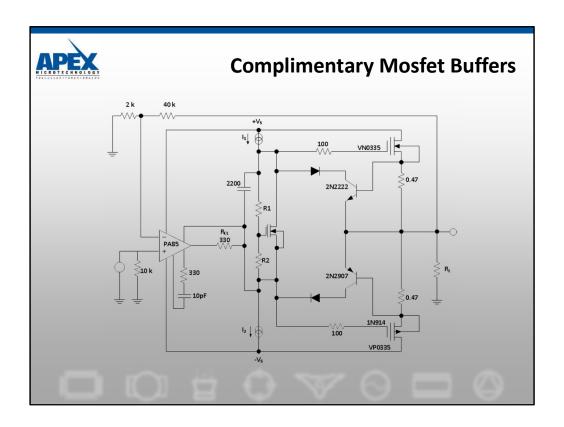

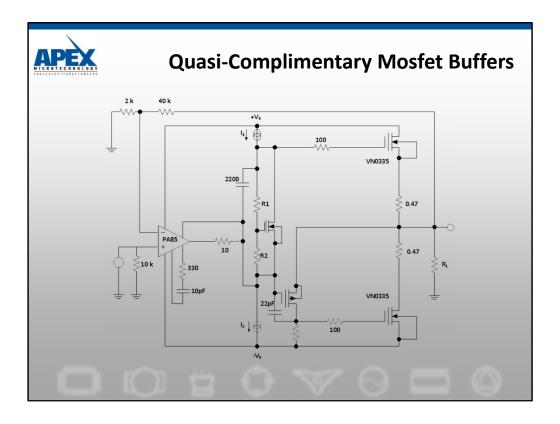

Class "C" output stages tie the bases or gates of the power devices together. Omitting the usual bias network between these bases reduces cost with the penalty of increased crossover distortion.

Assuming a resistive load and the drive stage voltage in the range of ±0.6V. There is no output current because the power devices need about a Vbe to turn on. There is a dead band of about 1.2V which the driver must cross over before output current can change polarity. For MOSFET outputs this dead band is usually somewhere between 4 to 6V.

The good news is that because the output does not move, there is no feedback to the driver. It is running open loop during dead band transition and slews across as fast as it can. This means at low frequencies this distortion is quite low. Class "C" outputs are generally not recommended above 1KHz but this varies with tolerance of distortion.

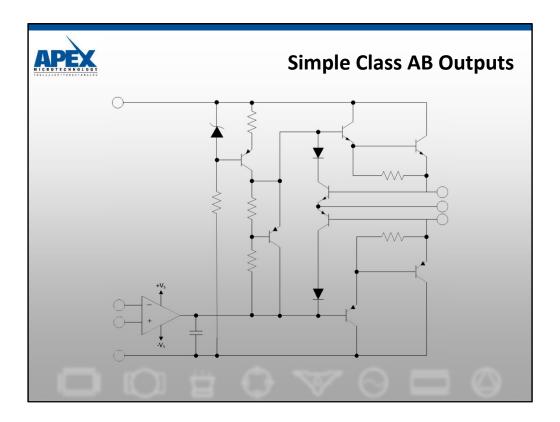

The class "AB" output keeps some current flowing in the output transistors at all times to minimize crossover distortion. This area is still the largest contributor to total harmonic distortion but the "dead" band is gone.

The circuit is known as a Vbe or Vgs multiplier. Think of this transistor as a noninverting op amp with the Vbe (Vgs) as an input and two about equal input and feedback resistors. If the multiplier transistor and the output transistors are tightly thermally coupled, distortion can be kept low and the possibility of thermal runaway is eliminated. This is one area where the hybrid really shines over a discrete circuit because these transistors are physically and thermally close to each. Many Apex amplifiers also use thermistors to compensate for tracking differences due to the transistors being different types. Imagine the tracking differences when the multiplier and power transistors are in separate packages.

We refer to this as a simple amplifier because of the monolithic driver stage which may incorporate 50 to 100 transistors on a single chip.

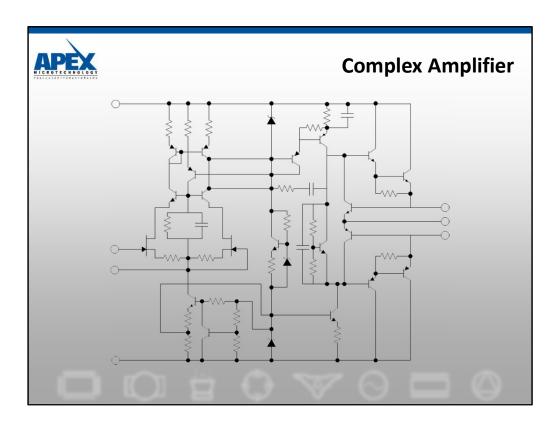

Here is the most difficult and costly way to build a power op amp. Monolithic driver candidates are often lacking in performance above  $\pm 15$ V and above  $\pm 40$ V the picture is down right discouraging. Being able to select each individual transistor for optimum overall performance of the power op amp results in DC accuracy under 1mV, speeds to 1000V/ $\mu$ s or total supply voltages to 1200V.

|    | A                         | В          | С          | D                               | E                           | F                           | G                                  | Н               | -1                     | J           |           | K        | L                             | М                             | N                                                  | 0        | P                | Q                             | R               |

|----|---------------------------|------------|------------|---------------------------------|-----------------------------|-----------------------------|------------------------------------|-----------------|------------------------|-------------|-----------|----------|-------------------------------|-------------------------------|----------------------------------------------------|----------|------------------|-------------------------------|-----------------|

| 1  | Part Selection            |            |            |                                 |                             | Read Me                     |                                    |                 | Slew rate to           | Fr          | equenc    | g conver | sion:                         |                               |                                                    |          |                  |                               |                 |

| 2  | Most positive peak output |            | 75         | Volts                           | -                           |                             |                                    | Slew rate       |                        | 130         | Vłus      |          |                               |                               |                                                    |          |                  |                               |                 |

| 3  | Most negative             | peak :     | output     |                                 | -75                         | Volts                       | Shown                              |                 | est                    | Frequency   | 2         | 75.86857 | KHz                           |                               | To the rig                                         | ht:      |                  |                               |                 |

| 4  | Output current            |            |            |                                 | 11                          | Amps                        | Amplifier                          |                 | 31 200                 |             |           |          |                               | Washers, sockets, cage jacks, |                                                    |          |                  |                               |                 |

| 5  | Frequency                 |            |            |                                 | 1                           | 1 KHz Slew rate = 0.47 Vłus |                                    | •               |                        |             |           |          | recommended Vs, typ slew rate |                               |                                                    |          |                  |                               |                 |

| 6  | DUAL                      |            |            |                                 |                             |                             |                                    | 1               |                        |             |           |          |                               |                               |                                                    |          |                  |                               |                 |

| 7  | Model                     | Vss<br>Min | Vss<br>Max | lout<br>Contin<br>uous<br>Max A | Vdrop<br>(Satura<br>tion V) | Com-<br>mon<br>Mode V       | Power<br>Band-<br>width KHz<br>Typ | iq<br>mA<br>Max | Int.<br>Power<br>W Max | Pkg Style   | Price USD |          | Voltage<br>Offset<br>mV max   | Drift<br>uV/°C                | Eval Kit Amplifier<br>Sold Type<br>Separ-<br>ately |          | Current<br>Limit | Ther-<br>mal<br>Shut-<br>down | Therm-<br>Washe |

| 8  | MSA240                    | 3          | 100        | 20                              | 2.8                         |                             | 5.0                                | 78              | 250                    | KC 58 pin   | \$        | 133,95   | 9                             |                               | EK56                                               | PVM Full | Adjust           | No                            |                 |

| 9  | MP240FC                   | 30         | 200        | 20                              | 9.2                         | 15                          | 31.8                               | 25              |                        | FC          | Ť         | \$151.50 | 5                             | 50                            | EK52                                               | Op Amp   | Adjust           | No                            |                 |

| 10 | MP240FC+Vb                | 6          | 200        | 20                              | 3.3                         | 15                          | 31.8                               | 25              | 170                    | FC          |           | \$151.50 | 5                             | 50                            | EK52                                               | Op Amp   | Adjust           | No                            |                 |

| 11 | MSA260                    | 3          | 450        | 20                              | 3.6                         |                             | 5.0                                | 20              | 250                    | KC 58 pin   | \$        | 199.35   | 9                             |                               | EK56                                               | PVM Full | Adjust           | No                            |                 |

| 12 | PA04                      | 30         | 200        | 20                              | 8.0                         | 8                           | 54.1                               | 90              | 200                    | CR (MO-127) | \$        | 315.00   | 10/5                          | 50/30                         | EK04                                               | Op Amp   | Adjust           | No                            | TW05            |

| 13 | PA04+Vb                   | 6          | 200        | 20                              | 5.5                         | 8                           | 54.1                               | 90              | 200                    | CR (MO-127) | \$        | 315.00   | 10/5                          | 50/30                         | EK04                                               | Op Amp   | Adjust           | No                            | TW05            |

| 14 | SA01                      | 16         | 100        | 20                              | 4.8                         |                             | 4.2                                | 78              | 185                    | DE (PD10)   | \$        | 452.35   | 10                            |                               | EK01                                               | PVM Full | Adjust           | Yes                           | TW10            |

| 15 | PA52                      | 24         | 200        | 40                              | 7.0                         | 12                          | 106.1                              | 36              | 400                    | CR (MO-127) | \$        | 557.70   | 10/5                          | 50                            | EK27                                               | Op Amp   | None             | No                            | TW05            |

| 16 | PA52+Vb                   | 6          | 200        | 40                              | 1.6                         | 12                          |                                    |                 | 400                    | CR (MO-127) | \$        | 557.70   | 10                            | 50                            | EK27                                               | Op Amp   | None             | No                            | TW05            |

| 17 | SA18                      | 16         |            |                                 | 1.9                         |                             | 2.3                                |                 |                        | CR (MO-127) | \$        |          |                               |                               | EK18                                               | PVM Half | Special          | Yes                           | TW05            |

| 18 | SA12                      | 16         |            |                                 | 7.7                         |                             | 20.0                               |                 |                        | CR (MO-127) | \$        |          |                               |                               | EK17                                               | PVMFull  | Adjust           | Yes                           | TW05            |

| 19 | SA03                      | 16         |            |                                 | 3.1                         |                             | 2.3                                |                 |                        | CR (MO-127) | \$        | 646.90   |                               |                               | EK03                                               | PVMFull  | Adjust           | Yes                           | TW05            |

| 20 | SA08                      | 16         |            | 20                              | 3.8                         |                             | 2.3                                |                 |                        | CR (MO-127) | \$        |          |                               |                               | EK15                                               | PVMFull  | Adjust           | Yes                           | TW05            |

| 21 | PA52A+Vb                  | 6          |            | 50                              | 1.3                         | 12                          |                                    |                 |                        | CR (MO-127) | \$        |          | 5                             |                               | EK27                                               | Op Amp   | None             | No                            | TW05            |

| 22 | PA03                      | 30         |            |                                 | 5.1                         | 10                          |                                    |                 |                        | CU (MO-127) | \$        |          |                               | 30/10                         | EK09                                               | Op Amp   | Fixed            | Yes                           | TW05            |

| 23 | MP38CL                    | 30         |            | 10                              | 9.1                         | 15                          |                                    |                 |                        | CL          | \$        | 71.05    | 10                            |                               | EK59                                               | Op Amp   | Adjust           | No                            | _               |

| 24 | MP38CL+Vb                 | 6          |            | 10                              | 7.3                         | 15                          |                                    |                 |                        | CL          | \$        | 71.05    | 10                            |                               | EK59                                               | Op Amp   | Adjust           | No                            | -               |

| 25 | MP108FD                   | 30         |            | 10                              | 10.2                        | 15                          |                                    |                 |                        | FD          | \$        | 127.20   | 5                             |                               | EK57                                               | Op Amp   | Adjust           | No                            | -               |

| 26 | MP108FD+Vb                | 6          | 200        | 10                              | 5.6                         | 15                          | 360.8                              | 65              | 100                    | FD          | \$        | 127.20   | 5                             | 50                            | EK57                                               | Op Amp   | Adjust           | No                            |                 |

Amplifier requirements have been entered into the yellow cells and the command button used to calculate suitability and sort by cost. For each parameter, the suitability ratio is 1 if the product meets (or exceeds) the requirements or is equal to requirement/capability. The sum of the ratios is used to sort the list.

In this example we see both switching and linear solutions meeting all the application requirements spanning more than a 5.5:1 price range. Vss min and max are data sheet specifications while +Vs and -Vs are estimations of supply requirements for this specific application (accounts for Vdrop or Saturation Voltage at the application output current). Note the blank cells where parameters do not apply to PWM amplifiers.

Here we find the MSA240 is the "best" choice. However, the selection process knows nothing about noise tolerance of the application, space and weight limitations for heatsink and filter inductors, duty cycle of the output signal, accuracy requirements, military screening needs or - - - -. This is a good tool, but we still need an engineer to complete the job.

Even though Dilbert would have a fit, we may even find that talking to marketing would be a good idea. Note the last few lines where the output current spec is shaded green because the amplifiers do not meet the application requirements. This indicates we may be able to reduce cost 2:1 if the output current specification could be reduced only 10%!

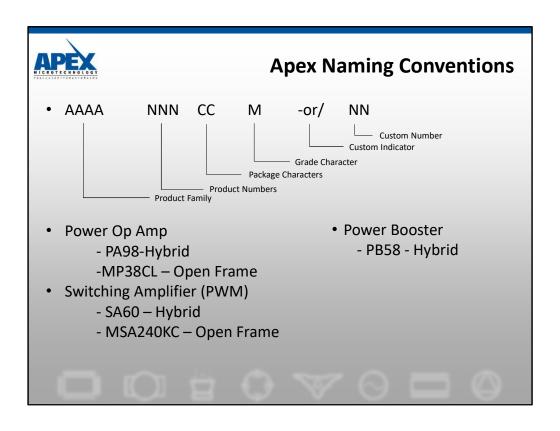

The overall naming convention for naming new products was adopted in mid- 2002. There will always be at least two alpha and two numeric characters plus two more alpha to define the package. The remaining characters are all optional. The most common grade characters are:

The "A" suffix indicates electrical grade out for improved DC accuracy and sometimes voltage capability, temperature range or speed.

The "M" suffix indicates a part with identical design to the standard but with hi-rel screening added. Various models are offered as non-compliant (Apex verified), /883 (government verified) or SMD (government verified and controls the drawing).

The PA and MP power op amps are indeed operational amplifiers following all the rules for these basic building blocks where in a properly designed circuit, performance is controlled by feedback rather than op amp parameters.

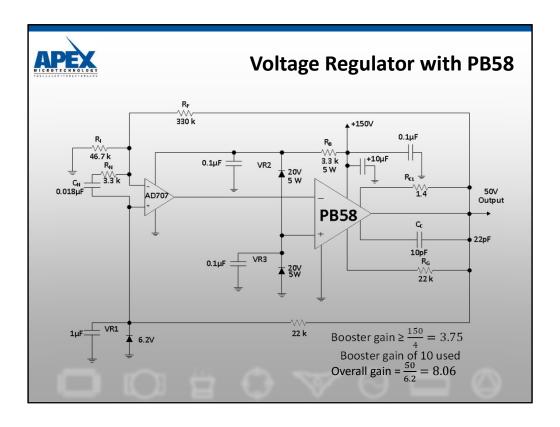

The PB power boosters are a unique cost effective solution providing a programmable gain from 3 to 25 at voltages up to  $\pm 150$ V and up to 2A. They are usually configured as the power stage of a composite amplifier which then acts like a power op amp. With the front end of the composite being a low cost typically  $\pm 15$ V op amp, speed and accuracy are easily tailored to need of the application.

The SA and MSA PWM amplifiers come to the rescue when internal power dissipation gets out of hand with linear devices. They provide one full bridge or one half bridge per package

### **Electrical Limitation**

Effects on the Amplifier

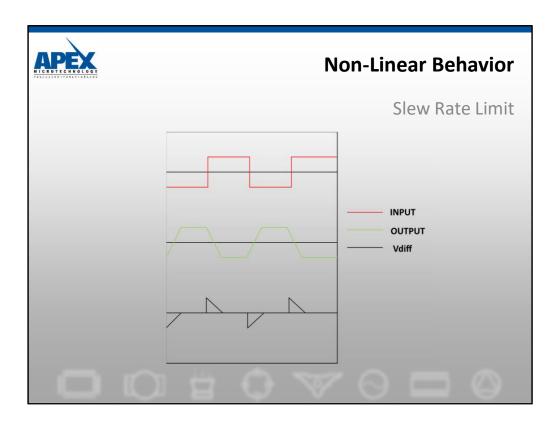

- Slew Rate Limiting

- Output Saturation

- Current Limiting

- Shut Down

- Common Mode Requirements

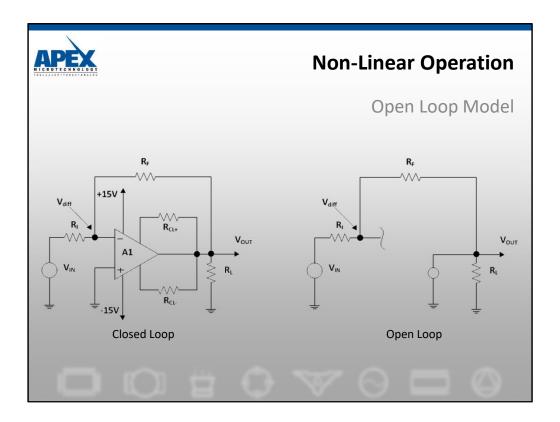

Power amplifiers and small signal op amps share many limitations. Understanding the limitations of a standard op amp will help you design more accurate, reliable circuitry. It helps to have a good understanding of what happens to an amplifier when it operates outside of its linear region. Most of these electric limitations can be traced to this common denominator

When an amplifier is operated in a closed loop it exhibits linear behavior. A violation of any of the limitations mentioned earlier will effectively open the loop. Once the loop is opened, Vin and Vout appear as two independent voltage sources. Rf and Ri function as a simple voltage divider between the two resistors. This voltage appears as a differential input voltage. In cases where the output stage is in a high impedance state, such as power off or thermal shutdown, Vout goes away and Vin is divided down by the series combination of Rin, Rf and Rload.

The effect of operating the amplifier in the slew limited region can be seen most dramatically by applying a step voltage to the input. Since the output of the amplifier cannot keep up with an infinite dV/dt, it goes into slew limited mode and begins changing its output voltage. At the point the amplifier goes into slew limit, we can use our "disappearing op amp" model to visualize what happens at the inverting input node of A1. In the example above, at t=0+, the input voltage has changed from +10 volts to - 10 volts, but the output voltage has not yet changed from -10 volts. Therefore, -10 volts will be on both sides of the divider comprised of RF and RI. Since there is no voltage difference, the full -10 volts will appear as VDIFF. As the output tries to "catch up", the right side of the divider will be changing linearly to +10 volts, therefore the differential voltage will drop linearly until the output catches up with the input. When the output catches up, the loop is closed and the differential voltage is zero.

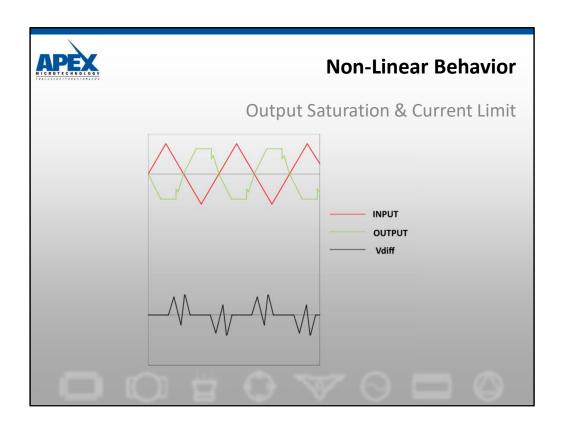

Output saturation and current limit exhibit similar behavior — clipping on the amplifier output. This clipping produces differential input voltages. Any type of clipping can result in an overdriven condition internal to the amplifier. This can lead to recovery problems ranging from simple long recovery to ringing during recovery.

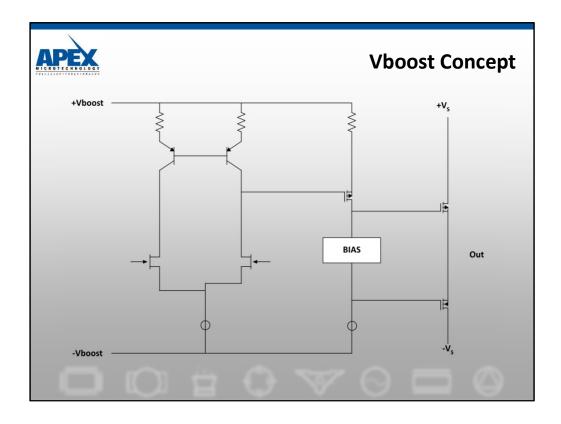

The Vboost concept separates the supplies of the front end, or driver stage, from the supplies of the output stage. When the Vboost supply magnitudes are larger than those of the Vs supplies, the output power MOSFETs can be driven closer to saturation. This allows lower voltages for the high power supply for a given output voltage requirement, thus increasing efficiency and reducing heatsink requirements.

Additionally, the higher Vboost voltages allow a wider range of common mode voltage on the inputs. This can be especially valuable when paralleling amplifiers. While the Vs supplies will be rated for many amperes, it is rare that the Vboost supplies need to be rated over 100mA.

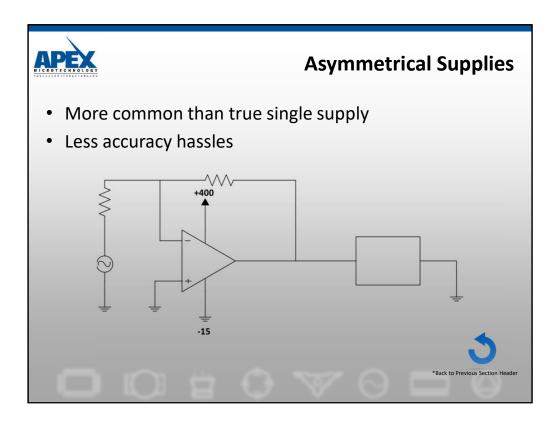

This is especially true of asymmetrical supply circuits with reactive loads - discussed in more detail later in the presentation. Consider a capacitive piezo drive circuit with symmetric slew rates that drives from 0-100V. Traditional asymmetric supplies might be -15 and 115V. In order to charge and discharge the capacitance symmetrically, these supplies need to be rated for the full current. With the Vboost feature, the -15V can be applied to – Vb and -Vs is tied directly to GND, still allowing an output voltage of 0-100V. –Vb need only to be rated for the input stage Iq of the amplifier.

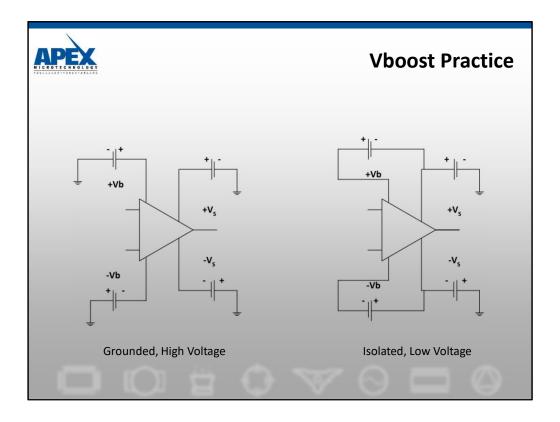

On the left, we see simple ground referenced Vboost supplies which are 5 to 20V larger in magnitude than the Vs supplies. While these supplies do not carry the multiple ampere output currents, they do need to support amplifier quiescent current.

On the right, the Vboost still needs to supply amplifier quiescent current, but with voltage ratings of only 5 to 20V, the wattage requirement will be substantially lower than the ground referenced topology. Sometimes, truly isolated supplies will be used, but converter circuits tied directly to the Vs supplies are very common

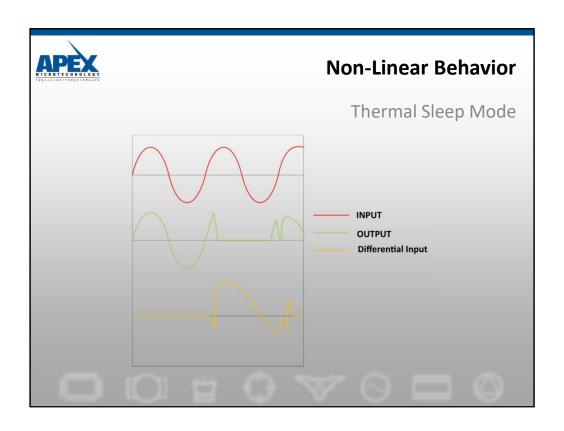

The situation with sleep mode is similar to thermal shutdown. In both cases, the amplifier is disabled by some circuitry which results in the output going into a high impedance state. One additional caution is that when coming out of sleep mode, an amplifier may saturate to one of the rails before recovering.

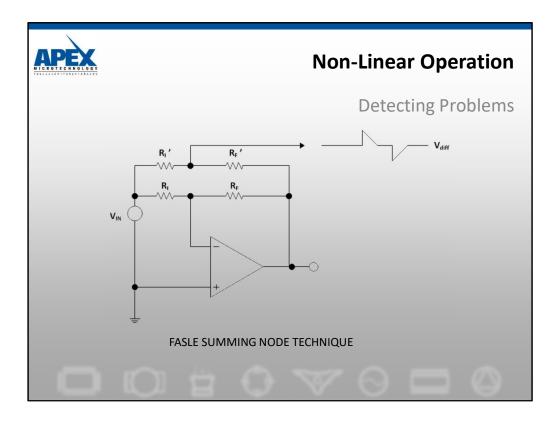

The common denominator of all non-linear modes of operation is the appearance of differential input voltages. One method of sensing when an amplifier is in a non-linear region is to use this false summing node technique.

If Rf"/Ri'=Rf/Ri, then Vdiff equals the voltage at the inverting node of the amplifier. This buffered error voltage signal can be used as an error flag possibly to drive a logical latch that could shut down the system.

## **ABS Maximums vs. The Spec Table**

- Absolute Maximum Ratings

- Stress levels, applied one at a time, will not cause permanent damage

- Does NOT guarantee op amp performance

- Specifications

- Linear operation ranges

- Vos, Ib, drift, CMRR...guaranteed performance

Beware that one stress level may bring on a second, which calls off all bets on op amp survival. Consider a commercial part where the last line of the specification table called "TEMPERATURE RANGE,case" is listed as -25/+85°C. Even though the ABS MAX temperature is 125°C, the part may latch up (very large voltage offset) at 86°C. With loads such as DC coupled inductors this may also lead to violation of the SOA.

| 1                                     |                 |     |      |       |     | Dat                 | tasl            | hee   | et,   |

|---------------------------------------|-----------------|-----|------|-------|-----|---------------------|-----------------|-------|-------|

| MP108 • MP108A                        | APEX            |     |      |       |     |                     |                 |       |       |

| ABSOLUTE MAXIM                        | JM RATINGS      |     |      |       |     |                     |                 |       |       |

| Parameter                             |                 | Sy  | mbol | Min   |     | Max                 |                 | Units |       |

| SUPPLY VOLTAGE, +V <sub>s</sub> to -V | /s              |     |      |       |     | 20                  | 0               | 1     | /     |

| SUPPLY VOLTAGE, +V <sub>B</sub>       | (Note 6)        |     |      |       |     | +V <sub>S</sub> , - | +15             | 1     | /     |

| SUPPLY VOLTAGE, -V <sub>B</sub>       | (Note 6)        |     |      |       |     | -V <sub>S</sub> , - | 15              | 1     | /     |

| OUTPUT CURRENT, peak, w               | ithin SOA       |     |      |       |     | 12                  |                 | 1     | 4     |

| POWER DISSIPATION, intern             |                 |     |      |       |     | 100                 | 0               | V     | ٧     |

| INPUT VOLTAGE                         |                 |     |      |       |     | +V <sub>B</sub> to  | -V <sub>B</sub> | 1     | /     |

| TEMPERATURE, pin solder,              | 10s             |     |      |       |     | 22                  | 5               | °(    | -     |

| TEMPERATURE, junction                 |                 |     |      |       |     | 150                 |                 | °C    |       |

| TEMPERATURE, storage                  |                 |     |      | -40   |     | +105                |                 | °C    |       |

| OPERATING TEMPERATUR                  | E RANGE, case   |     |      | -4    | 0   | +8                  | 5               | °(    | С     |

| SPECIFICATIONS                        | Test Conditi    | ons |      | MP108 |     | Min                 | MP108A          |       |       |

| INPUT                                 | (Note 1)        |     | Min  | Тур   | Max | Min                 | Тур             | Max   | Units |

| OFFSET VOLTAGE                        |                 |     |      | 1     | 5   |                     |                 | 3     | mV    |

| OFFSET VOLTAGE, vs. temperature       | Full temp range |     |      | 50    |     |                     |                 |       | µV/°C |

| OFFSET VOLTAGE, vs. supply            |                 |     |      |       | 20  |                     |                 |       | μV/V  |

Absolute Maximum specification are found at the top of the second page of every Apex datasheet. Guaranteed specifications can be found below the absolute max specs.

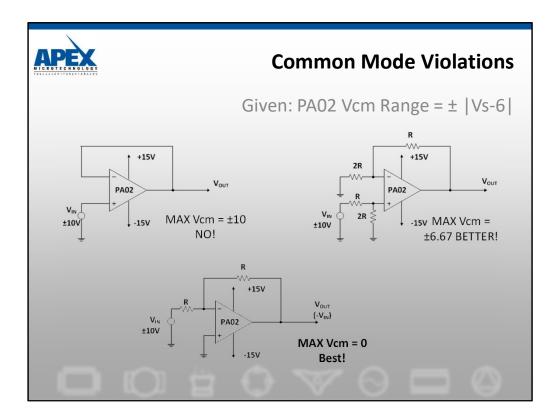

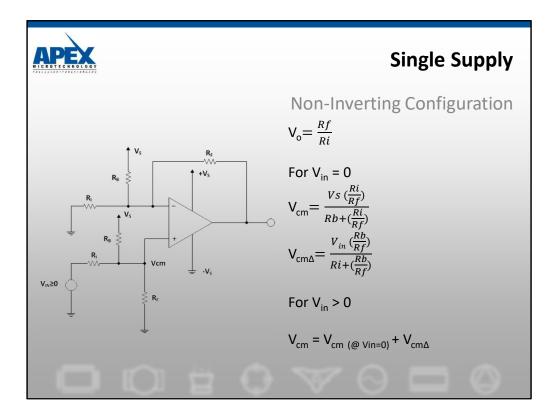

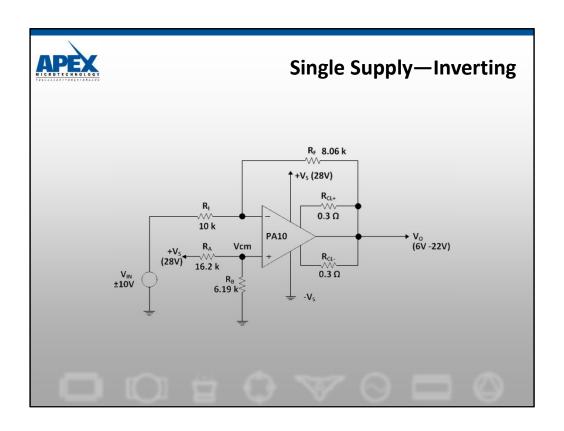

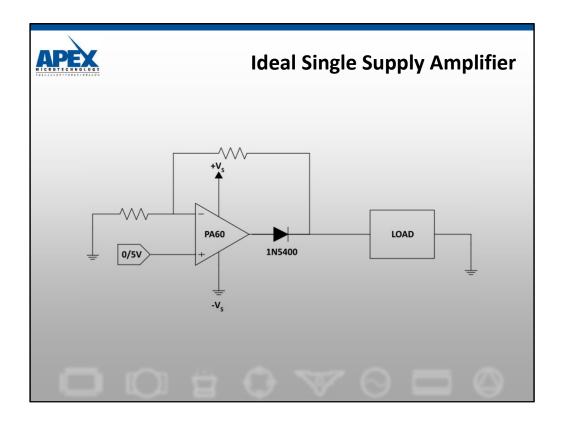

In an inverting configuration, the op amps non-inverting terminal is usually tied to ground, making the inverting terminal a "virtual ground." This results in zero common mode voltage: a desirable benefit. However, operating the amplifier in a non-inverting mode results in the common mode voltage being equal to the voltage at the non-inverting terminal.

The schematics above illustrate the problem. The amplifier used in this example cannot have any common mode voltage that approaches within 6 volts of either supply rail. The first example shows a unity gain follower. This is the configuration where common mode violations are most common. Note that the input voltage is equal to the common mode voltage. In our example the input voltage exceeds the common mode range.

In the second example the input signal is first attenuated and then gained back up to result in a lower common mode voltage but a unity gain non-inverting transfer function. That is: Vo = Vi(2R/(2R+R))(1+Rf/Ri) where Rf = R and Ri = 2R

The third example shows the best approach to eliminating common mode violations: use inverting configurations. In this case the input voltage is still 10 volts, the output voltage is 10 volts, but the common mode voltage is zero, eliminating the problem. Of course this does invert the phase of the output signal.

# **Amplifier Protection**

Electrical

- Input Transients

- Output Transients

- Over-voltage

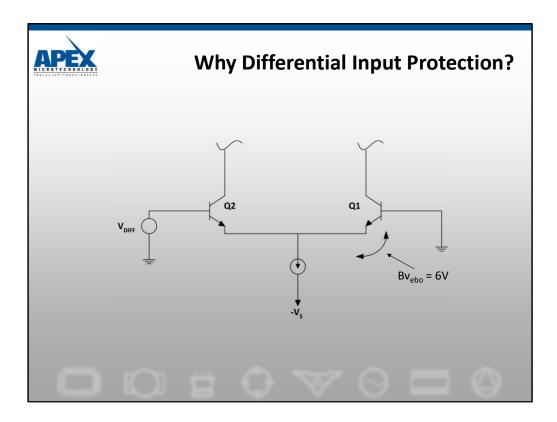

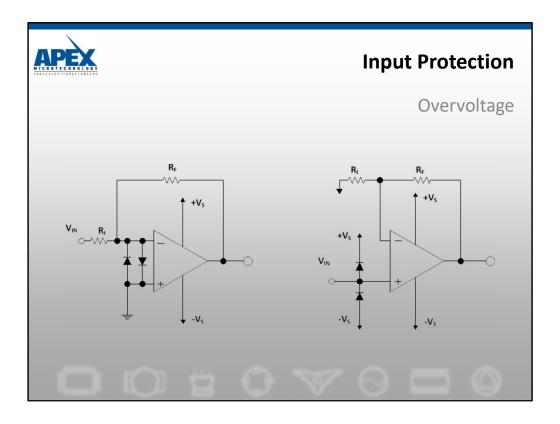

#### WHY DIFFERENTIAL INPUT PROTECTION?

Simple, to avoid damaging input stages due to differential overstress. Any input stage has maximum differential limits that can be exceeded any number of ways, with the most subtle occurring during non-linear operation.

In amplifiers with bipolar inputs, such as a PA12, differential overload has the additional hazard of causing degradation without catastrophic failure. Exceeding the reverse-bias zener voltage of a base-emitter junction of a transistor used in a differential amplifier can permanently degrade the noise, offset, and drift characteristics of that junction.

The protection scheme on the left uses parallel diodes to limit the differential voltage and uses series resistors to limit the current that flows through the diodes. The slightly more complicated scheme on the right accomplishes the same thing, but by using stacked diodes, allows a higher differential voltage to be developed. This allows a greater slew rate overdrive. The capacitors perform a similar function by allowing high frequency information to be passed directly to the input terminals.

Ref. AN1 AMPLIFIER PROTECTION AND PERFORMANCE LIMITATIONS AN25 HIGH VOLTAGE AMPLIFIER SUPPORT COMPONENTS

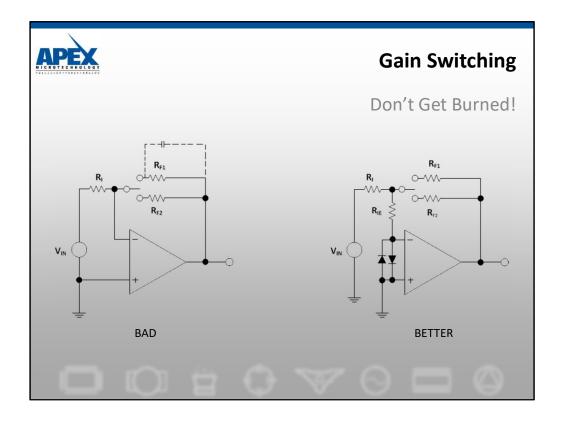

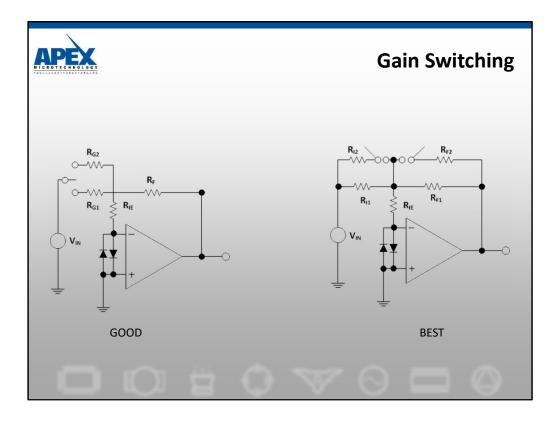

Often it is a requirement that the gain of an amplifier be switchable. This is very common in ATE applications. One method of doing this is shown on the left. This is a very poor way to accomplish gain switching. The problem is that the amplifier is usually much faster than the relay used to switch between the two resistors. WHEN THE RELAY OPENS, THE AMPLIFIER HAS NO FEEDBACK. Since the amplifier is now open loop, the amplifier will immediately slew toward one of the supply rails. By the time the relay closes, the amplifier will be saturated and the output voltage will appear directly at the inverting terminal of the amplifier.

The method on the right does not solve the problem, but it does provide amplifier protection. The parallel diodes clamp the differential input voltage while Rie limits the amount of current that can flow during transient conditions. The value of Rie should be chosen to limit the current to approximately 15mA with one full supply voltage across the resistor.

Ref. AN1 AMPLIFIER PROTECTION AND PERFORMANCE LIMITATIONS

The "good" approach above represents a vast improvement over the previous technique. In this approach, gain is switched by switching the value of the input resistors rather than the feedback resistor. The major advantage to this approach is that the feedback loop is kept closed at all times. When the relay opens, the amplifier is now a unity gain follower with a zero volt input. The most voltage that will appear at the output is the offset of the amplifier. Input protection is still shown in this configuration to protect against possible switching transients.

The "best" approach above shows a configuration that prevents switching inside the feedback loop or opening up the input loop. Ri1 and Rf1 are in place at all times. The gain of the circuit is switched by EITHER switching in Ri2 to parallel Ri1 OR by switching in Rf2 to parallel Rf1. This approach eliminates any transient voltages due to relay switching. At the time of contact closure, only the gain changes. Although input protection is still shown in this schematic, its only function is to protect the input in cases of non-linear operation, such as slew rate or current limit.

Ref. AN1 AMPLIFIER PROTECTION AND PERFORMANCE LIMITATIONS

In multiple power supply systems, power supply sequencing is often a problem. If the power supplies for the "driving stage" come up before the "driven stage", the maximum input common mode specification may be violated. The diodes shown in the two circuits above serve to clamp the driven input to the amplifier supply pin so that the input cannot be raised above the supply voltage. Note, however, that if the supplies are in a high impedance state when the power supply is turned off, this approach will not protect the amplifier. Under those conditions however, the inverting amplifier configuration could be protected by running parallel diodes from the inverting node to ground. These would clamp the inverting input to ground under any circumstances. Since the inverting terminal is normally at virtual ground, these diodes would not interfere with signal in any way. However, on the non-inverting amplifier this approach will not work because the non-inverting input sustains a common mode voltage.

Ref. AN1 AMPLIFIER PROTECTION AND PERFORMANCE LIMITATIONS

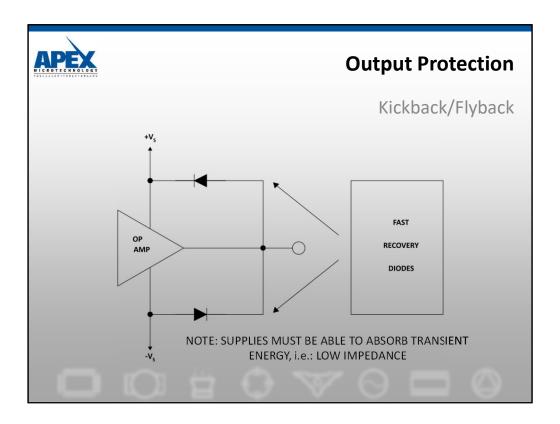

Attempting to make a sudden change in current flow in an inductive load will cause large voltage flyback spikes. These flyback spikes appearing on the output of the op amp can destroy the output stage of the amplifier. DC motors can produce continuous trains of high voltage, high frequency kickback spikes. In addition, piezo-electric transducers not only generate mechanical energy from electrical energy but also vice versa. This means that mechanical shocks to a piezo-electric transducer can make it appear as a voltage generator. Again, this can destroy the output stage of an amplifier.

Although most power amplifiers have some kind of internal flyback protection diodes, these internal diodes SHOULD NOT be counted on to protect the amplifier against sustained high frequency kickback pulses. Under these conditions, high speed, fast recovery diodes should be used from the output of the op amps to the supplies to augment the internal diodes. These fast recovery diodes should be under 100 nanoseconds recovery time; and for very high frequency energy, should be under 20 nanoseconds. One other point to note is that the power supply must look like a true low impedance source or the flyback energy coupled back into the supply pin will merely result in a voltage

spike at the supply pin of the op amp again leading to an over voltage condition and

Ref. AN1 AMPLIFIER PROTECTION AND PERFORMANCE LIMITATIONS

AN25 HIGH VOLTAGE AMPLIFIER SUPPORT COMPONENTS

possible destruction of the amplifier.

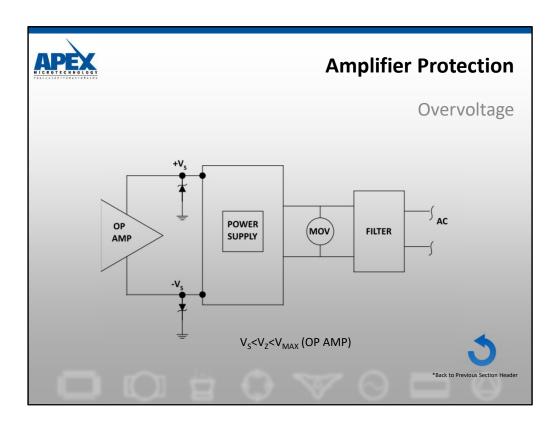

The amplifier should not be stressed beyond its maximum supply rating voltage. This means that any condition that may lead to this voltage stress level should be protected against. Two possible sources are the high energy pulses from an inductive load coupled back through flyback diodes into a high impedance supply or AC main transients passing through a power supply to appear at the op amp supply pins. These over voltage conditions can be protected against by using zeners or transorbs direct from the amplifier supply pins to ground. The rating of these zeners whould be greater than the maximum supply voltage expected, but less than the breakdown voltage of the operation amplifier. Note also that MOS's can be included across the input to the power supply to reduce transients before they reach the power supply. Low pass filtering can be done between the AC main and the power supply to cut down on as much of the high frequency energy as possible. Note that inductors using power supplies will pass all high frequency energy and capacitors used in power supply are usually large electrolytics which have a very high ESR. Because of this high ESR, high frequency energy will not be attenuated fully and therefore will pass on through the capacitor largely unscathed.

Ref. AN1 AMPLIFIER PROTECTION AND PERFORMANCE LIMITATIONS

AN25 HIGH VOLTAGE AMPLIFIER SUPPORT COMPONENTS

# **Safe Operating Area**

Output Stage Danger!

- Current Handling Limitations

- Thermal (Power) Limitations

- Steady State

- Transient/Pulse Operation

- Second Breakdown

- Bipolar Devices

- MOSFETs: Not Applicable

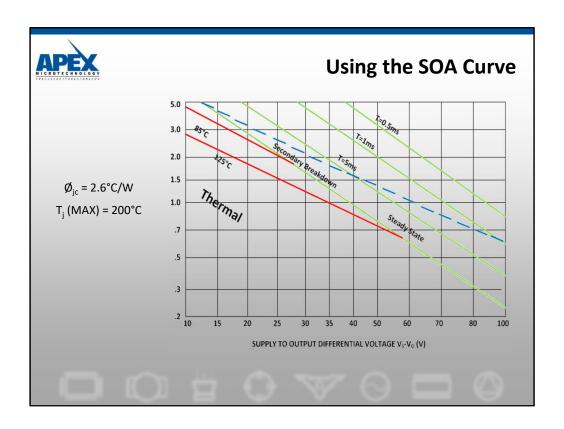

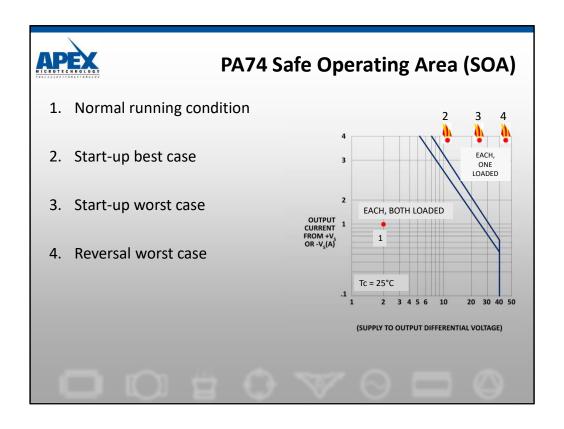

Safe operating area curves show the limitations on the power handling capability of power op amps. There are three basic limitations.

The first limitation is total current handling capability. A horizontal line or the top of the SOA curve and represents the limit imposed by conductor current handling capability die junction area and other current density constraints. The second limitation is total power handling capability or power dissipation capability of the complete amplifier. This includes both of the power die and the package the amplifier is contained in. Note that the product of output current on the vertical axis and Vs-Vo on the horizontal axis is constant over this line. The third portion of the curve is the secondary breakdown areas. This phenomenon is limited to bipolar devices. MOSFET devices do not have this third limitation. Secondary breakdown is a combined voltage and current stress across the device.

Although the constant current boundary and the secondary breakdown boundary remain constant, the constant power/thermal line moves toward the origin as case temperature increases. This new constant power line can be determined from the de-rating curves on the data sheet. The case temperature is primarily a function of the heat sink used.

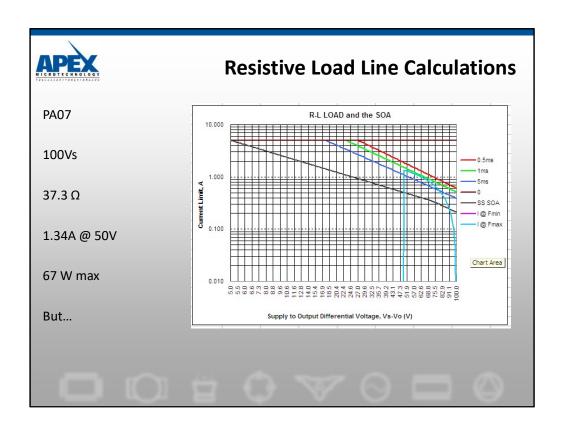

The dashed line was constructed in this manner for  $Tc = 25^{\circ}C$  for an amplifier advertised as a 67W device (PA07 or PA10). In addition to the fact that very few applications exhibit  $Tc=25^{\circ}$ , secondary breakdown prohibits DC operation over its entire length!

On the SOA graph, the horizontal axis,  $V_S - V_O$  does not define a supply voltage or total supply voltage or the output voltage. IT DEFINES THE VOLTAGE STRESS ACROSS THE CONDUCTING DEVICE. Thus  $V_S - V_O$  is the difference from the supply to the output across the transistor that is conducting current to the load. The vertical axis is simply the current being delivered to the load.

For resistive loads maximum power dissipation in the amplifier occurs when the output is 1/2 the supply voltage. This is because when the output is at 0 volts, no current flows from the amplifier whereas at maximum load current very little voltage is across the conducting transistor since the output voltage is near the supply voltage.

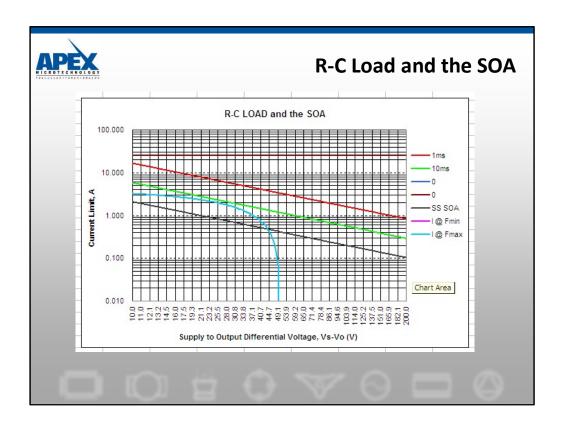

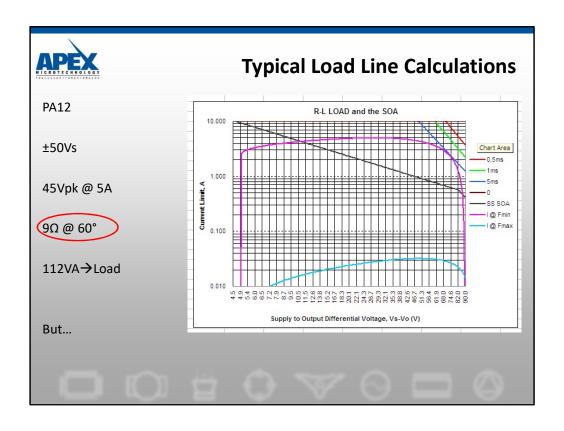

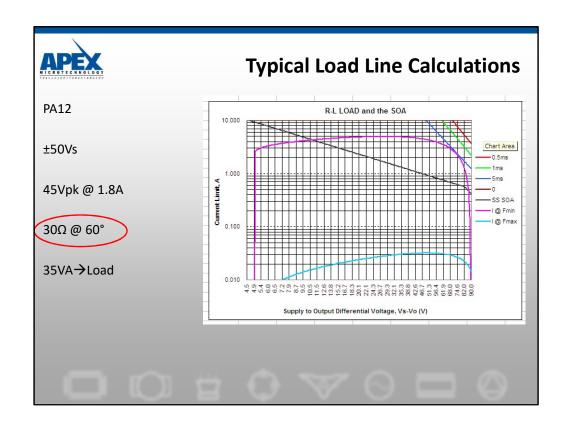

For reactive loads this is not the case. Voltage/current phase differences can result in higher than anticipated powers being dissipated in the amplifier.

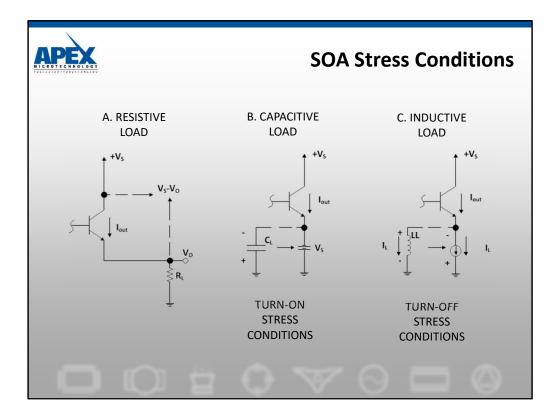

An example of an excessive stress condition created by a capacitive load is shown in Figure B. In this case the capacitive load has been charged to  $-V_s$ . Now the amplifier is given a "go positive" signal. Immediately the amplifier will deliver its maximum rated output current into the capacitor which can be modeled at t=0 as a voltage source. This leads to a stress across the conducting device of Imax X total supply voltage( $2V_s$ ).

Figure C shows a similar condition for an inductive load. For this situation we imagine the output is near the positive supply and current through the conductor has built up to some value IL. Now the amplifier is given a "go negative" signal which causes the output voltage to swing to down near the negative supply. However the inductor at time t=0 can be modeled as a current source still drawing IL. This leads to the same situation as before, that is total supply voltage across a device conducting high current.

Ref. AN1 SAFE OPERATING AREA, AN22

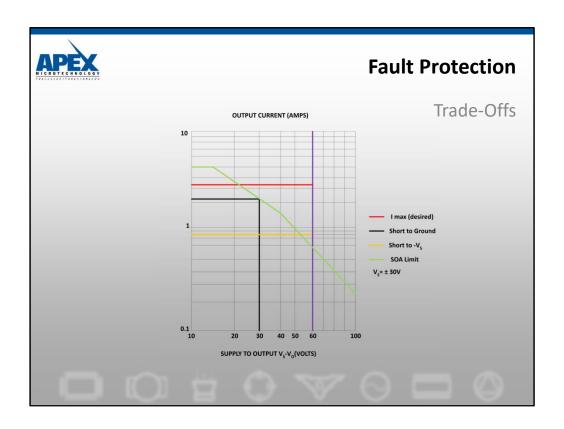

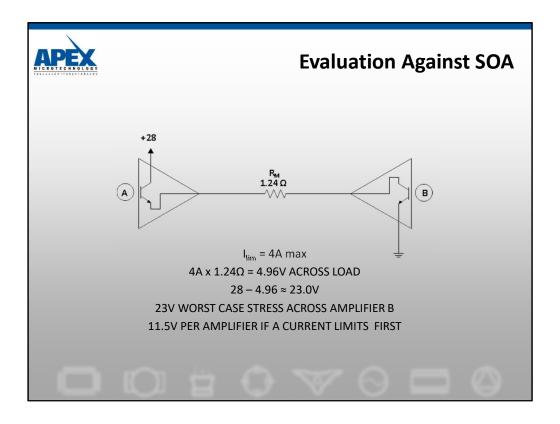

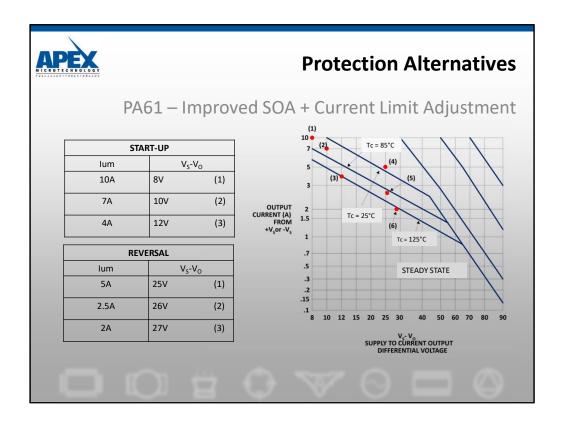

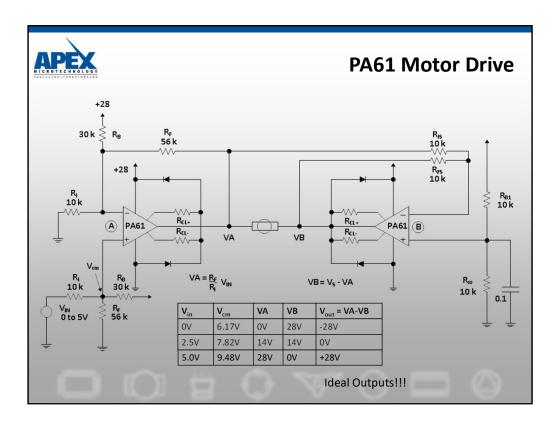

Current limit can be used to protect the amplifier against fault conditions. If, for instance, it is desired to protect the amplifier against a short-to-ground fault condition the Vs-Vo number on the horizontal axis is equal to Vs since Vo is zero. Following this value up to the power dissipation limit and then across to the output current gives the value of current limit necessary to protect the amplifier at that case temperature. Note that better heat sinking allows higher values of current limit.

For more aggressive fault protection it may be desired to protect the amplifier against short to either supply. This requires a significant lowering of current limit. For this type of protection, add the magnitudes of the two supplies used, find that value on the Vs-Vo axis, follow up to the SOA limit for the case temperature anticipated, then follow across to find the correct value of current limit.

It is often the case that requirements for fault protection and maximum output current may conflict at times. Under these conditions there are only four options. The first is simply to go the an amplifier with a higher power rating. The second is to trim some of the requirements for fault protection. The third is to reduce the requirement for maximum output current. The fourth option is a special type of current limit called "foldover" or "foldback." This is available on some amplifiers such as the PA10 and PA12.

Ref. AN1 SAFE OPERATING AREA, AN22

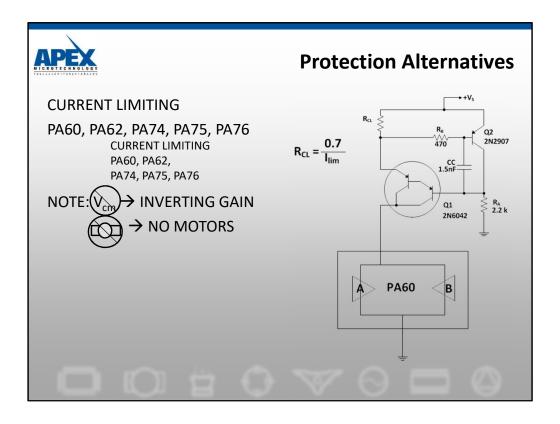

### **Current Limit Definition**

A way to force output voltage where ever needed to maintain constant output current.

- A non-linear mode of operation

- $V_{OUT} = f(I_{LIMIT} \text{ and } Z_{LOAD})$

- I<sub>LIMIT</sub> is only one term of the power equation

Current limit circuits do what their name implies but they are not magic cures for all load fault conditions. The non-linear operation (the op amp is unable to satisfy input signal/feedback demands) means monitoring the inputs for the presence of a differential voltage will signal this mode of operation.

Usually the current limit mode will reduce the output voltage but this is not always true. To determine critical survival the worst case voltage stress across the conducting transistor must be determined.

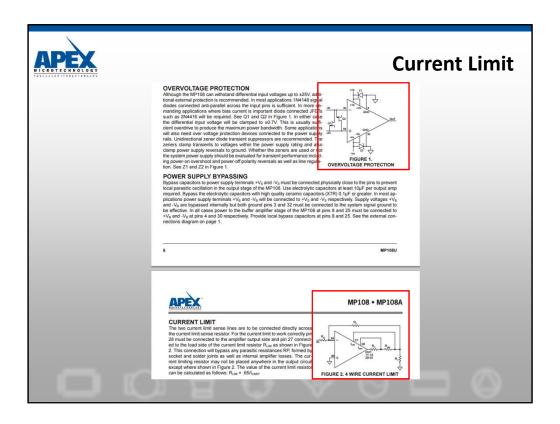

There are several different internal schemes used to implement current limit in Apex products. Most datasheets will have a formula or some text explaining the implementation used for the product. If there is no formula or reference, refer to application note 1.

Note that in most cases, all of the output current flows through the current limit resistor. Use  $I^2 * R$  to determine the power rating for the resistor

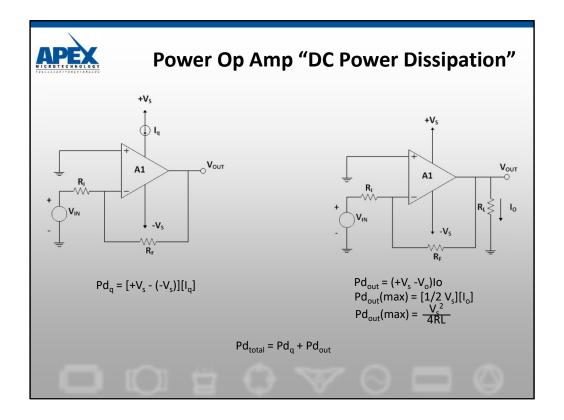

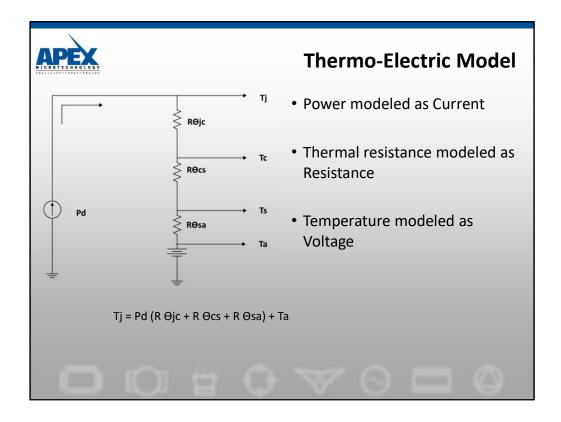

When calculating power dissipation in an amplifier, you MUST NOT FORGET THAT POWER DISSIPATION IN THE AMPLIFIER IS NOT EQUAL TO POWER DISSIPATION IN THE LOAD. That is, most of the time. One exception is when the output voltage is half of the supply voltage and the load is resistive. In this particular case the power dissipations are equal.

Calculating power dissipation in an amplifier under DC conditions with a resistive load is very simple.

The first portion of power dissipation is due to the quiescent power that the amplifier dissipates simply by sitting there with +Vs and –Vs applied. Multiplying total supply voltage by quiescent current gives the value of this power dissipation.

The maximum power dissipation in the amplifier under DC conditions with a resistive load is when the output voltage is 1/2 of the supply voltage. Therefore, whatever current is delivered to the load at 1/2 supply voltage multiplied by 1/2 supply voltage gives maximum power dissipation in the amplifier. The total dissipation is the sum of these two.

Ref. AN1 INTERNAL POWER DISSIPATION AND HEATSINKING

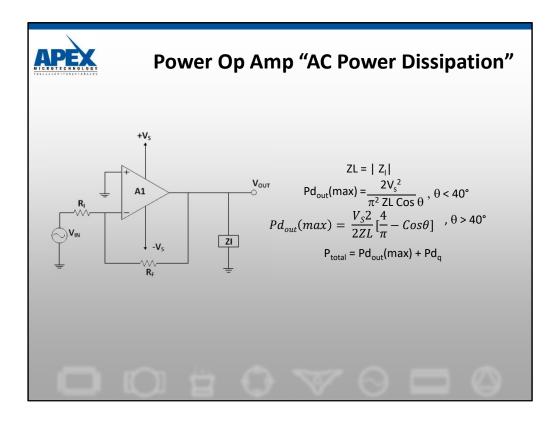

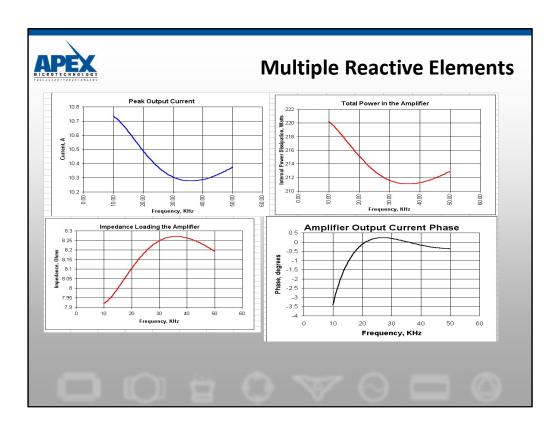

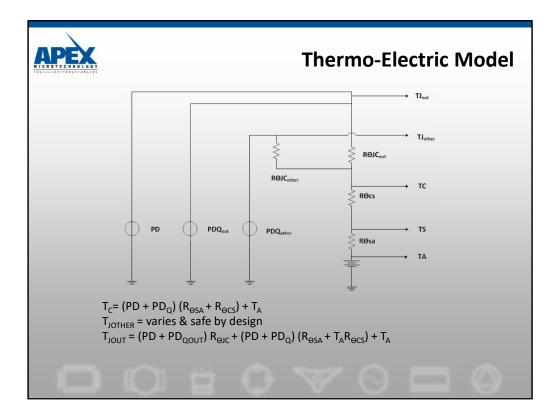

With an AC output and/or reactive loads, output power dissipation calculations can get a bit stickier. Several simplifying assumptions keep the problem reasonable for analysis. The actual internal dissipation can be determined analytically or through thermal or electrical bench measurements. Both Application Note 22 and Application Note 1 General Operating Considerations give details on measuring AC power dissipation.

Worst case AC power dissipation formulae are given above for any reactive load range. With these worst case formulae one can calculate worst case power dissipation in the output stage for AC drive conditions and reactive loads. For most power op amps output stage power dissipation is the dominant component of total power dissipation so adding worst case AC output power dissipation with DC quiescent power dissipation and using AC  $R\theta$ jc AC thermal

impedance for junction to case, will be sufficient for heatsink calculations.

Ref. AN1 INTERNAL POWER DISSIPATION AND HEATSINKING

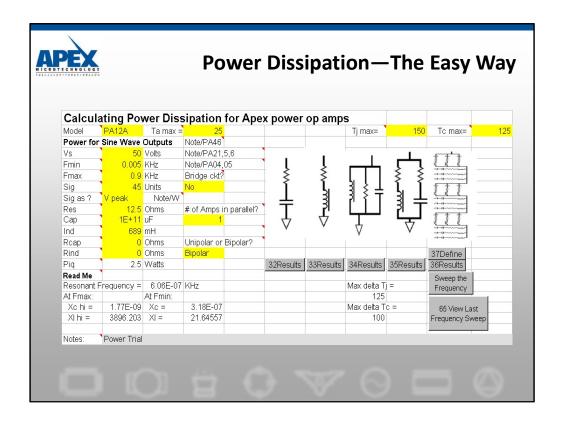

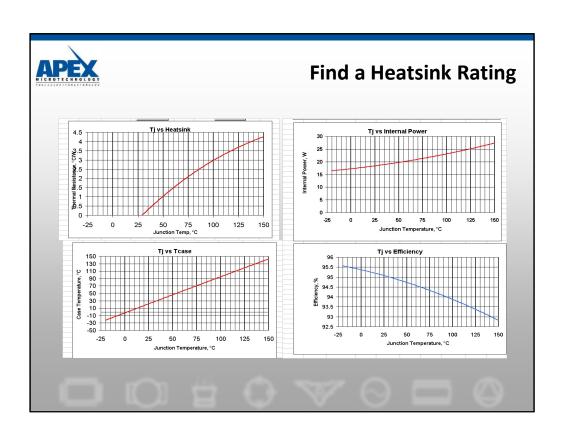

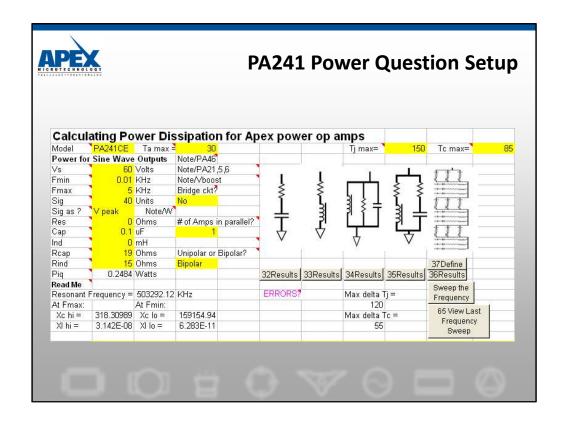

If your application can be modeled as a sine wave of any frequency, this sheet will tell you a lot. Entering a model pulls up a sizable portion of the data sheet for calculation and flag raising. Enter the three temperatures: ambient from the application, case per data sheet max or lower, and junction per contract or philosophy on reliability. If you need DC response, anything below 60Hz is OK. Define your output signal in terms of volts, amps or watts. If your load can be modeled by one of the first four diagrams, enter the values below. If you need diagram 5, use the Define Load command button.

#### Be sure to check these three cells!

If the Bridge circuit cell is "Yes", the signal and load values specified will be treated as total but internal power will be for a single op amp.

Internal power will be divided by the # of parallel amplifiers.

"Unipolar" forces only one power supply and the use of DC thermal resistance.

A few useful pieces of information show up on this screen along with a red flag if your specified supply voltage is out of bounds. For more answers use the command button below the desired load diagram.

Ref. AN37

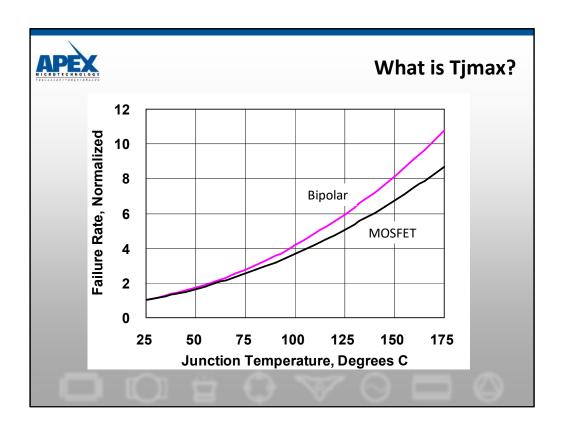

While this author would be the first to agree MIL-HDBK-217 has a few quirks and is very often misused, it does have the curves sloping in the right direction. Electronics is similar to your car, toaster--almost anything, even engineers! Run it too hot and it dies an early death. Apex suggests a maximum of 150°C for normal commercial applications. If the equipment is remotely located or down time is extremely expensive a lower temperature is appropriate.

This graph represents the temperature acceleration factors from revision F, Notice 2.

Ref. AN1 INTERNAL POWER DISSIPATION AND HEATSINKING

|                        |           |                                         |          |                     |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | â    |

|------------------------|-----------|-----------------------------------------|----------|---------------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|                        | At Fmin:  | At Fmax:                                |          | At Fmin:            | At Fmax:   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

| Z in Ohms              | 15915.50  | 21.87                                   |          | Maximu              |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

| Phase angle            | -89.95    | -46.70                                  |          | 39.6                | 37.8       | Vpk                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      |

| RMS Amperes            | 0.0012218 | 0.8891318                               | 1        | 28.001429           | 26.728636  | Vrms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |

| Peak Amperes           | 0.0017279 | 1.2574223                               | ļ        | 0.0017594           | 1.2221521  | Arms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |

| RMS Volts              | 19.445436 | 19.445436                               | >        | 0.0492652           |            | Wrms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |

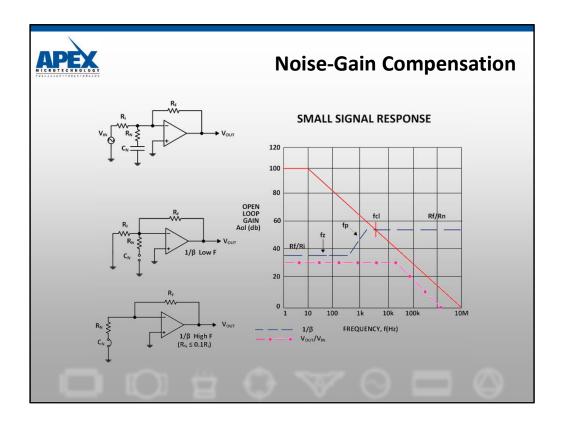

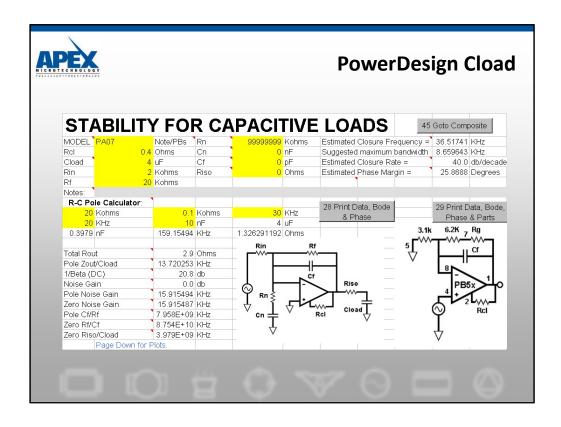

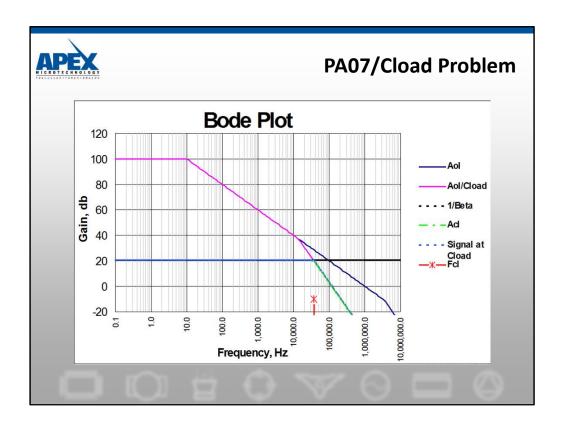

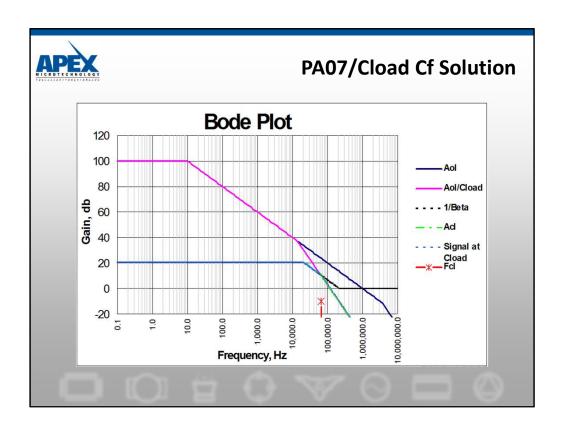

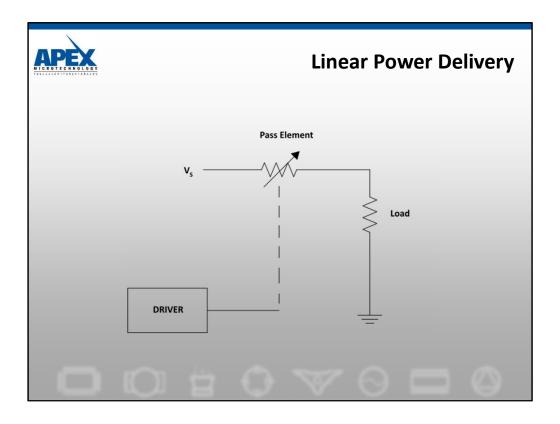

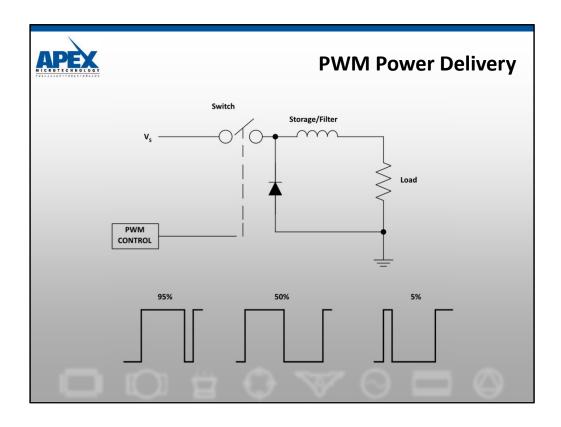

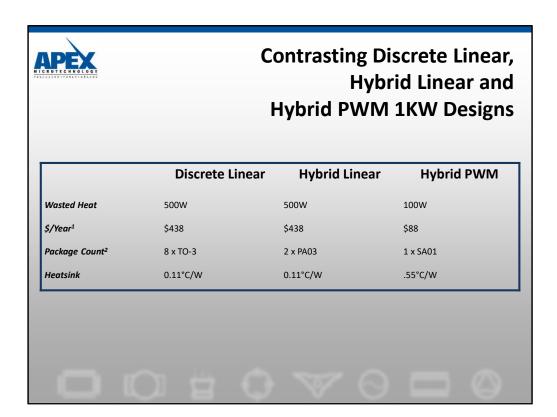

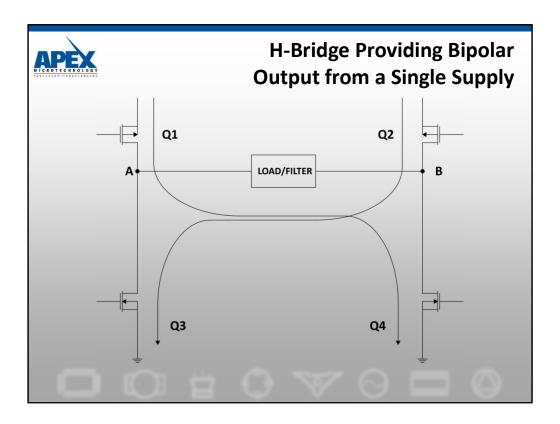

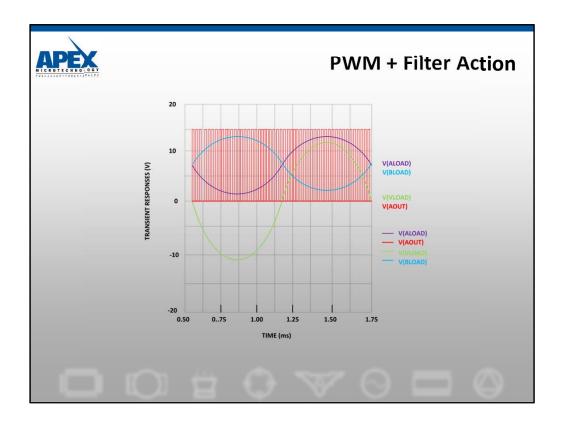

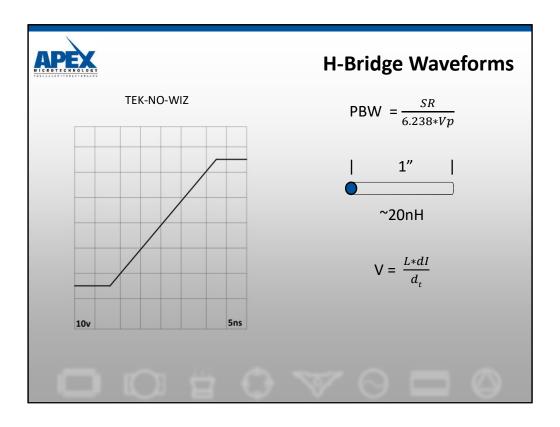

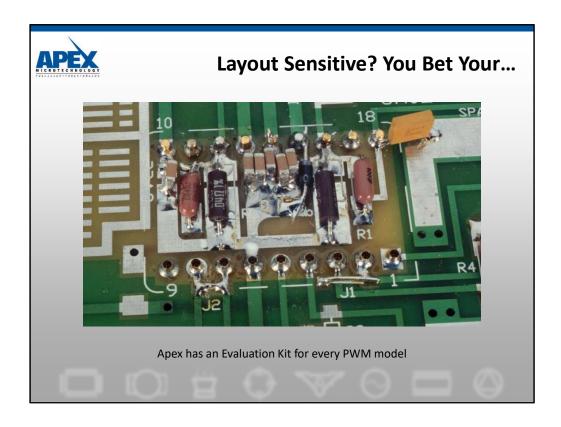

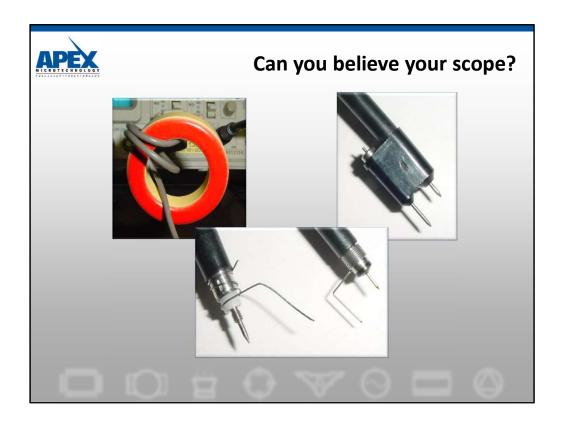

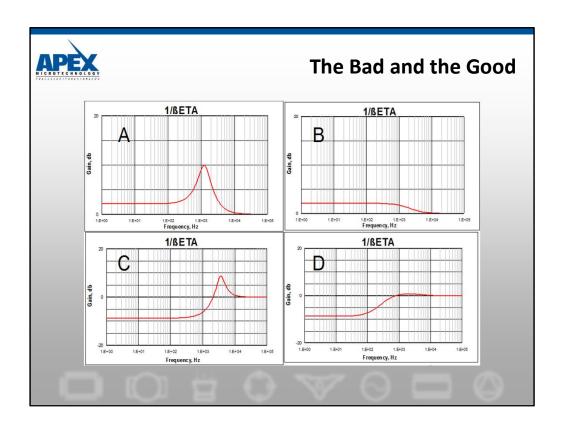

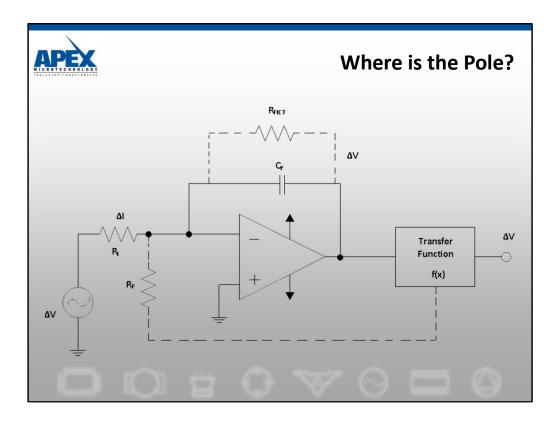

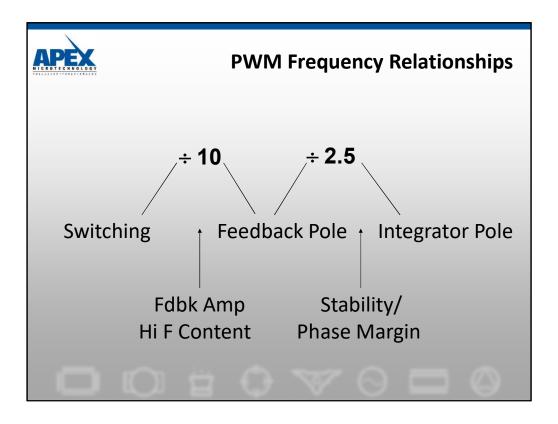

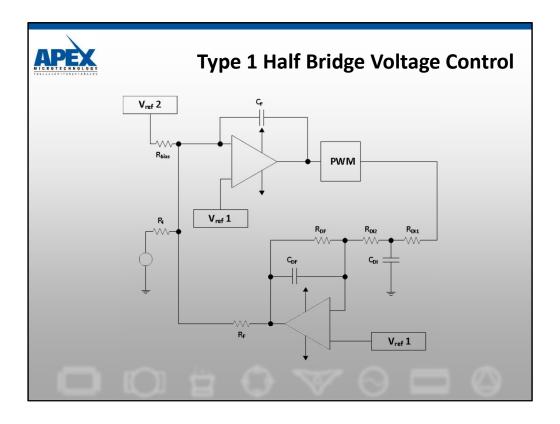

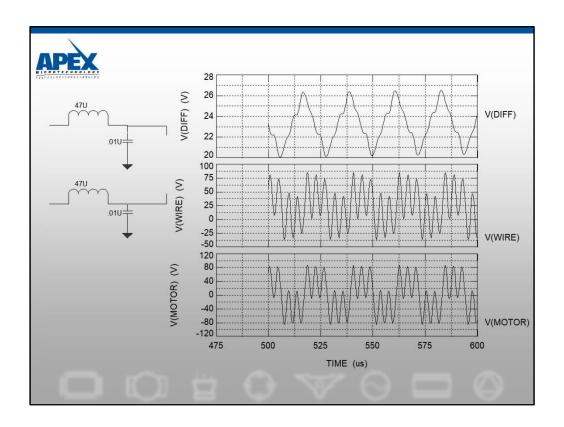

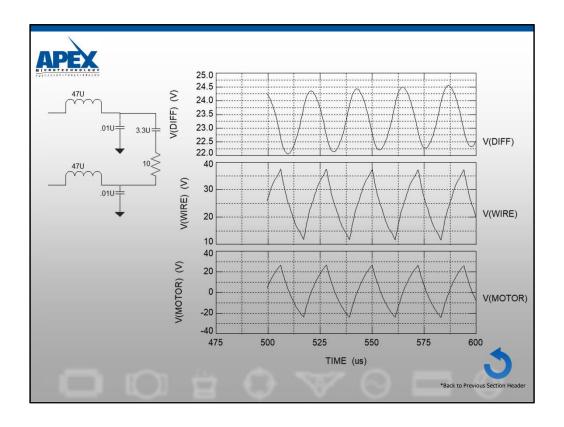

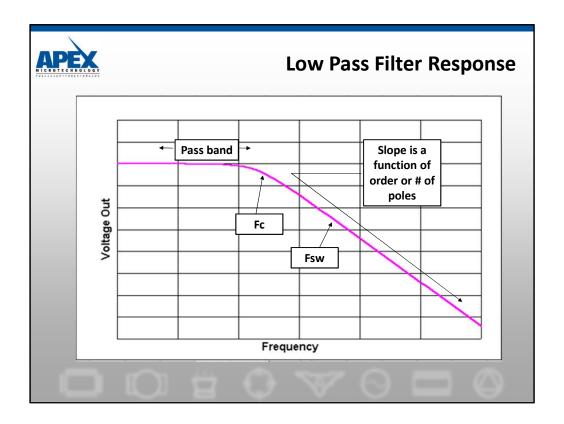

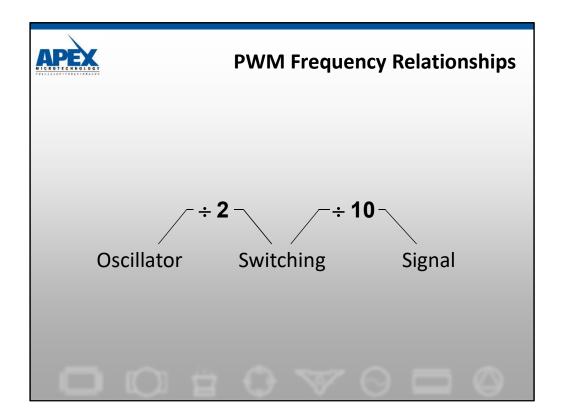

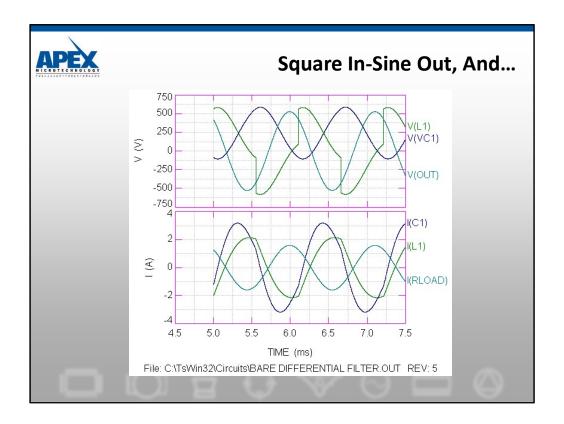

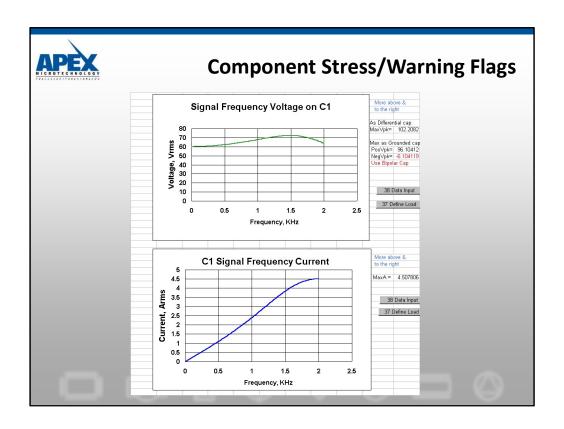

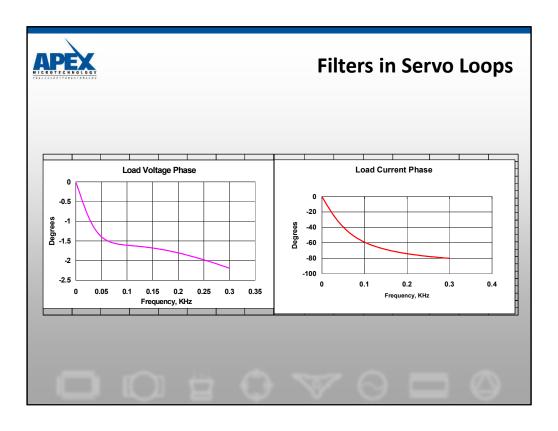

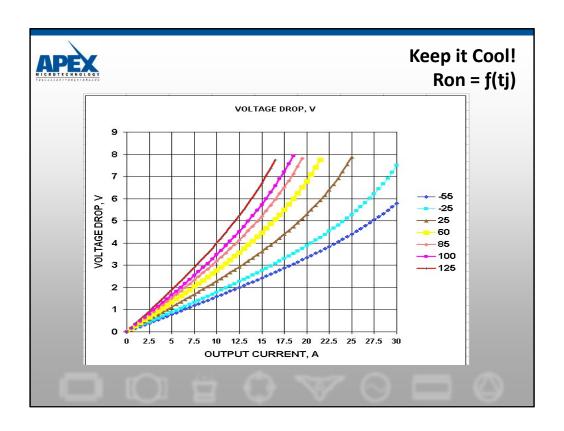

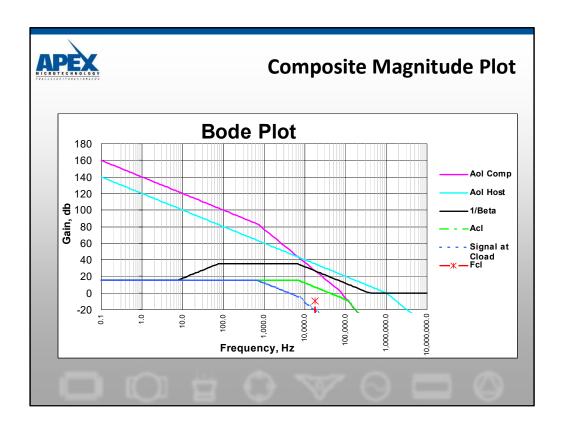

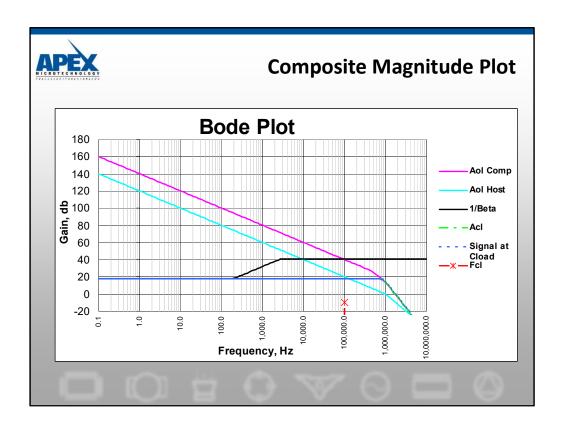

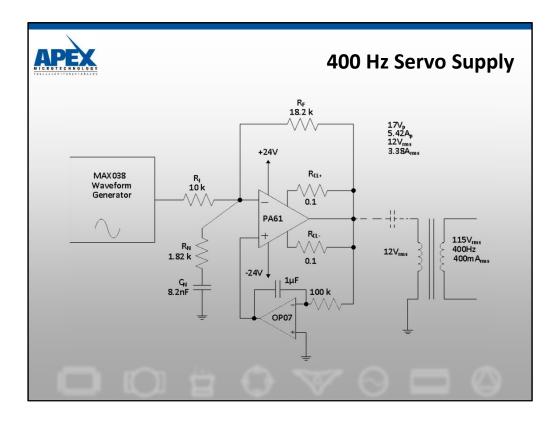

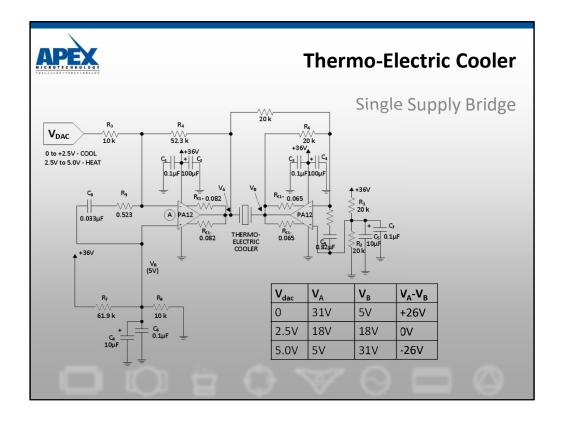

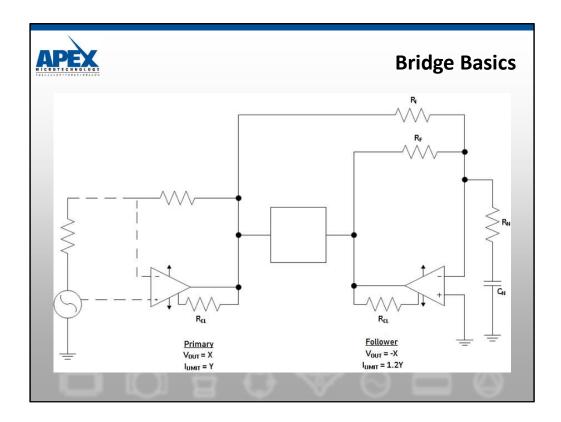

| Peak Volts             | 27.5      | 27.5                                    | >        | 4.643E-05           | 22.404837  | Wtrue                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |